Simulink Design Verifier использует формальные методы, чтобы идентифицировать скрытые ошибки проектирования в моделях. Это обнаруживает блоки в модели, которые приводят к целочисленному переполнению, мертвой логике, нарушениям доступа к массиву и делению на нуль. Это может официально проверить, что проект удовлетворяет функциональные требования. Для каждой ошибки проектирования или нарушения требований, это генерирует тест симуляции для отладки.

Simulink® Design Verifier™ генерирует тесты для покрытия модели и пользовательских целей расширить существующие основанные на требованиях тесты. Эти тесты управляют вашей моделью, чтобы удовлетворить условие, решение, изменил условие/решение (MCDC) и пользовательские цели покрытия. В дополнение к целям покрытия можно задать пользовательские цели тестирования, чтобы автоматически сгенерировать основанные на требованиях тесты.

Рабочий процесс Simulink Design Verifier обеспечивает рабочий процесс для Simulink Design Verifier. В частности, это описывает как к:

Усильте генерацию теста и поддержку поиска ошибок проектирования Simulink Design Verifier в рабочем процессе Модельно-ориентированного проектирования

Упростите бесшовное функционирование возможности генерации теста инструмента Simulink Design Verifier.

Оцените полноту и соответствие сгенерированных тестов.

При использовании программного обеспечения Simulink Design Verifier, чтобы усилить сертификацию или кредит проверки, предоставленный IEC Certification Kit, необходимо выполнить этот рабочий процесс как часть полного ISO 26262, IEC 61508, EN 50128, или жизненный цикл безопасности программного обеспечения IEC 62304.

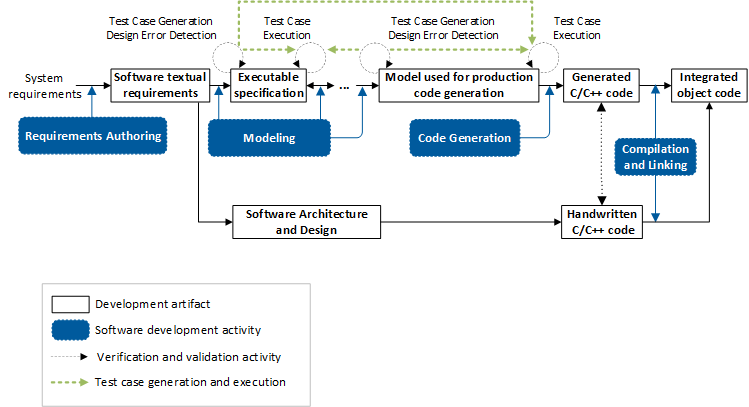

Рабочий процесс Simulink Design Verifier описывает генерацию теста и поддержку поиска ошибок проектирования Simulink Design Verifier как часть процесса Модельно-ориентированного проектирования. Можно использовать возможность генерации теста сгенерировать тесты для исполняемой спецификации, модель, используемая для генерации производственного кода или любой другой временной модели, созданной во время фазы моделирования. Можно использовать сгенерированные тесты, чтобы стимулировать исполняемую спецификацию или другой этап рабочего процесса Модельно-ориентированного проектирования. Можно использовать возможность поиска ошибок проектирования обнаружить мертвую логику, переполнение данных целочисленной или фиксированной точки, деление на нуль и нарушения заданных промежуточных минимальных и максимальных значений.

Следующее изображение иллюстрирует интегрирование Simulink Design Verifier в рабочий процесс Модельно-ориентированного проектирования IEC Certification Kit.

Simulink Design Verifier в рабочем процессе модельно-ориентированного проектирования

Чтобы получить доступ к документу Рабочего процесса Simulink Design Verifier, откройте Менеджера артефактов. Под Simulink Design Verifier, открытым файл certkitiec_sldv_workflow.pdf.