Переставьте вводимые символы путем выбора элементов матрицы по диагоналям

Блокируйте подбиблиотеку Чередования

Блок Matrix Helical Scan Interleaver выполняет чередование блоков путем заполнения матрицы со строкой вводимых символов строкой и затем отправки матричного содержимого в выходной порт спиральным способом. Number of rows и параметры Number of columns являются размерностями матрицы, которую блок использует внутренне для его вычислений.

Спиральный вид означает, что блок выбирает выходные символы путем выбора элементов по диагоналям матрицы. Число элементов в каждой диагонали совпадает с параметром Number of columns, после того, как блок перенесется мимо ребер матрицы при необходимости. Блок пересекает диагонали так, чтобы индекс строки и индекс столбца оба увеличения. Каждая диагональ после первой начинает одну строку ниже первого элемента предыдущей диагонали.

Параметр Array step size является наклоном каждой диагонали, то есть, суммы, которой увеличивается индекс строки, как индекс столбца увеличивается одним. Этот параметр должен быть целым числом между нулем и параметром Number of rows. Если параметр Array step size является нулем, то блок не чередуется, и вывод совпадает с входом.

Этот блок принимает на вход сигнал в виде вектора - столбца или скалярной величины. Число элементов входного вектора должно быть продуктом Number of rows и Number of columns.

Блок принимает следующие типы данных: int8, uint8, int16, uint16, int32, uint32, boolean, single, double и фиксированная точка. Выходной сигнал наследовал свой тип данных от входного сигнала.

Количество строк в матрице, которую блок использует для его вычислений.

Количество столбцов в матрице, которую блок использует для его вычислений.

Наклон диагоналей, которые читает блок.

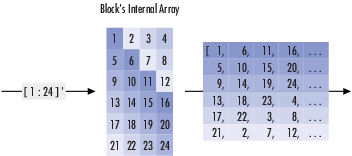

Если Number of rows и параметры Number of columns равняются 6 и 4, соответственно, то interleaver использует 6 4 матрица для ее внутренних вычислений. Если параметр Array step size равняется 1, то диагонали находятся как показано в фигуре ниже. Положения с тем же цветом являются частью той же диагонали, и диагонали с более темными цветами предшествуют, те с легче раскрашивают выходной сигнал.

Учитывая входной сигнал [1:24]', блок производит вывод

[1; 6; 11; 16; 5; 10; 15; 20; 9; 14; 19; 24; 13; 18; 23;... 4; 17; 22; 3; 8; 21; 2; 7; 12]