Обнаружьте истинную длительность на входе и создайте вывод истинная длительность на основе выходного типа

Simulink Design Verifier

True duration сигнала — Последовательные временные шаги, во время которых сигнал верен

Length истинной длительности сигнала — количество временных шагов, которые составляют истинную длительность

Фаза Input detection — фаза, которая завершена на итоговом временном шаге ожидаемой длины входа истинная длительность

Фаза Output construction — фаза, когда блок создает истинную длительность при выводе на основе выходного типа блока

Delay duration — Количество временных шагов задержки после входного обнаружения, после которого выходной сигнал верен

Вводы и выводы блока Detector имеют булев тип.

На входном обнаружении блок Detector создает выходной сигнал на основе одного из двух выходных типов, которые вы задаете:

Delayed Fixed Duration — После того, как входное обнаружение завершено и после того, как дополнительная задержка, выходной сигнал станет true для постоянного числа временных шагов. Истинная длительность вывода независима от входа.

Synchronized — В итоговом временном шаге входного обнаружения вывод становится true и остается true, пока входной сигнал продолжает быть true. Истинная длительность вывода отличается и синхронизируется с истинной длительностью входа.

Задайте, может ли блок быть сброшен к запуску входного обнаружения внешним булевым сигналом сброса.

Выберите Delayed Fixed Duration (значение по умолчанию), чтобы задать фиксированную истинную продолжительность длительности для вывода после дополнительной задержки. Выберите Synchronized, чтобы синхронизировать вывод истинная длительность с тем из входа.

Продолжительность истинной длительности для входного обнаружения (минимумом является 1).

Для Delayed Fixed Duration опционально задайте продолжительность длительности задержки, после которой вывод становится верным.

Для Delayed Fixed Duration задайте продолжительность вывода истинная длительность (минимумом является 1).

В следующих примерах используйте шаг расчета второго 1.

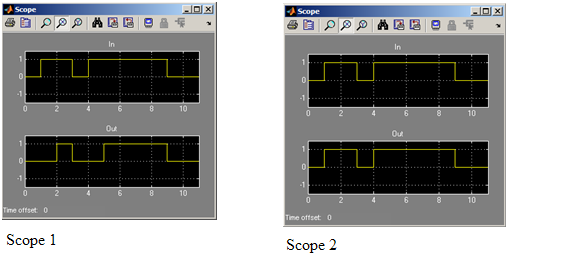

В этом примере, с набором Output type к Delayed Fixed Duration, входная фаза обнаружения не продолжается во время конструкции выходного сигнала. Следующие параметры блоков для блока Detector установлены можно следующим образом:

Time steps for input detection = 2

Time steps for delay (optional) = 1

Time steps for output duration = 2

Определите объем 1, показывает сценарий, где вторая длительность true не обнаруживается, потому что некоторые временные шаги true происходят во время выходной конструкции.

Однако вторая длительность true в Осциллографе 2 обнаруживается, потому что остающаяся длительность true после выходной конструкции удовлетворяет количество шагов, требуемых для входного обнаружения.

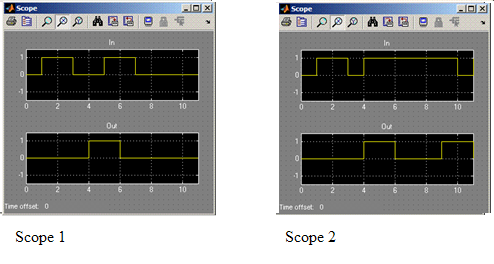

В этом примере, с набором Output type к Synchronized и набором Time steps for input detection к 2, вывод становится true в последнем шаге входного обнаружения. Вывод продолжает быть верным, пока входным сигналом является true.

Определите объем 1, показывает, что вывод становится верным на шаге второго раза, который является итоговым временным шагом входной фазы обнаружения. Когда номер временных шагов для входного обнаружения определяется к 1, вывод идентичен входу, как вы видите в Осциллографе 2.