Для проектов, которые требуют больших наборов данных доступа от внешней памяти, смоделируйте свой алгоритм с упрощенным Основным протоколом AXI4. Когда вы запускаете рабочий процесс IP Core Generation, HDL Coder™generates ядро IP с Основными интерфейсами AXI4. Интерфейс AXI4 Master может передать между вашим проектом и контроллером внешней памяти IP при помощи Основного протокола AXI4.

Можно использовать упрощенный Основной протокол AXI4, чтобы сопоставить с Основными интерфейсами AXI4. Используйте упрощенный Основной протокол записи AXI4 для транзакции записи и упрощенный Основной протокол чтения AXI4 для транзакции чтения.

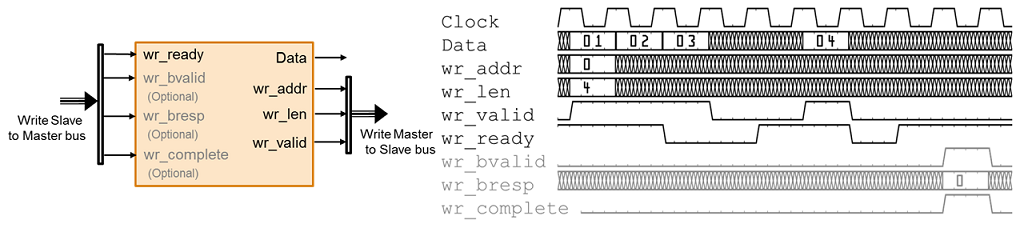

Эти данные показывают схему синхронизации для сигналов, что вы моделируете в интерфейсах ввода и вывода DUT для Основной транзакции записи AXI4.

DUT ожидает wr_ready, чтобы стать высоким, чтобы инициировать запрос записи. Когда wr_ready становится высоким, DUT может отослать запрос записи. Запрос записи состоит из сигналов Write Master to Slave bus и Data. Эта шина состоит из wr_len, wr_addr и wr_valid. wr_addr задает начальный адрес, в который DUT хочет записать. Сигнал wr_len соответствует количеству элементов данных в этой транзакции записи. Data может быть отправлен, пока wr_valid высок. Когда wr_ready становится низким, DUT должен прекратить отправлять данные в одном такте, и сигнал Data становится недопустимым. Если DUT продолжает отправлять данные после того, как один такт, данные будут проигнорированы.

Выходные сигналы

Смоделируйте Data и сигналы Write Master to Slave bus в DUT интерфейс вывода.

Данные: данные, которые вы хотите передать, допустимый каждый цикл транзакции.

Write Master to Slave bus, который состоит из:

wr_addr: Начальный адрес транзакции записи, которая выбирается в первом цикле транзакции.

wr_len: количество значений данных, которые вы хотите передать, выбранный в первом цикле транзакции.

wr_valid: Когда этот управляющий сигнал становится высоким, он указывает, что сигнал Data, выбранный при выводе, допустим.

Входные сигналы

Смоделируйте Write Slave to Master bus, который состоит из:

wr_ready: Этот сигнал соответствует противодавлению от ведомого IP оперативная или внешняя память. Когда этот управляющий сигнал идет высоко, он указывает, что данные могут быть отправлены. Когда wr_ready является низким, DUT должен прекратить отправлять данные в одном такте. Можно также использовать сигнал wr_ready определить, может ли DUT сразу отправить второй пакетный сигнал после того, как первый пакетный сигнал был отправлен. Несколько пакетных сигналов поддерживаются, что означает, что сигнал wr_ready остается высоким, чтобы сразу принять второй пакет после того, как последний элемент первого пакета был принят.

wr_bvalid (дополнительный сигнал): сигнал Ответа от ведомого ядра IP, что можно использовать в целях диагноза. Сигнал wr_bvalid становится высоким после того, как межсоединение AXI4 примет каждую пакетную транзакцию. Если wr_len больше, чем 256, Основной модуль записи AXI4 разделяет большой пакетный сигнал в пакеты 256 размеров. wr_bvalid становится высоким для каждого пакета 256 размеров.

wr_bresp (дополнительный сигнал): сигнал Ответа от ведомого ядра IP, что можно использовать в целях диагноза. Используйте этот сигнал с сигналом wr_bvalid.

wr_complete (дополнительный сигнал): Управляющий сигнал, который, когда остается высоким для одного такта, указывает, что транзакция записи завершилась. Этот сигнал утверждает в последнем wr_bvalid пакета.

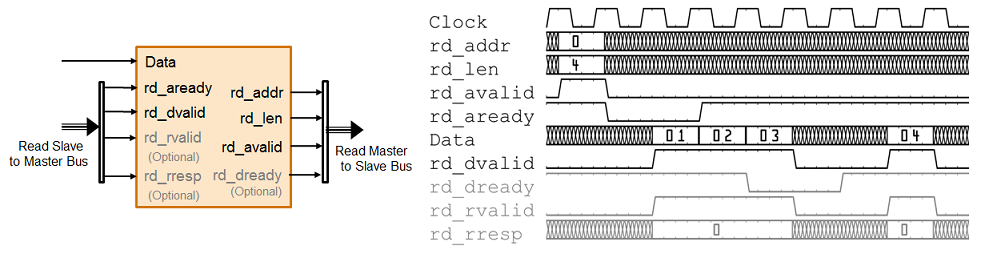

Эти данные показывают схему синхронизации для сигналов, что вы моделируете в интерфейсах ввода и вывода DUT для Основной транзакции чтения AXI4. Эти сигналы включают Data, Read Master to Slave Bus и Read Slave to Master Bus.

DUT ожидает rd_aready, чтобы стать высоким, чтобы инициировать запрос чтения. Когда rd_aready высок, DUT может отослать запрос чтения. Запрос чтения состоит из rd_addr, rd_len и сигналов rd_avalid Read Master to Slave bus. Ведомый IP или внешняя память отвечают на запрос чтения путем отправки Data в каждом такте. Сигнал rd_len соответствует количеству значений данных, чтобы читать. DUT может получить Data, пока rd_dvalid высок.

Считайте запрос

Чтобы смоделировать запрос чтения, в DUT интерфейс вывода, моделируют Read Master to Slave bus, который состоит из:

rd_addr: Начальный адрес для транзакции чтения, которая выбирается в первом цикле транзакции.

rd_len: количество значений данных, которые вы хотите считать, выбранный в первом цикле транзакции.

rd_avalid: Управляющий сигнал, который задает, допустим ли запрос чтения.

В интерфейсе входа DUT реализуйте сигнал rd_aready. Этот сигнал является частью Read Slave to Master bus и указывает, когда принять запросы чтения. Можно контролировать сигнал rd_aready определить, может ли DUT отправить последовательные пакетные запросы. Когда rd_aready становится высоким, он указывает, что DUT может отправить запрос чтения за следующий такт.

Считайте ответ

В интерфейсе входа DUT смоделируйте сигналы Read Slave to Master bus и Data.

Данные: данные, которые возвращены в запрос чтения.

Read Master to Slave bus, который состоит из:

rd_dvalid: Управляющий сигнал, который указывает, что Data, возвращенный в запрос чтения, допустим.

rd_rvalid (дополнительный сигнал): сигнал ответа от ведомого ядра IP, что можно использовать в целях диагноза.

rd_rresp (дополнительный сигнал): сигнал Ответа от ведомого ядра IP, которое указывает на состояние транзакции чтения.

В DUT интерфейс вывода можно опционально реализовать сигнал rd_dready. Этот сигнал является частью Read Master to Slave bus и указывает, когда DUT может начать принимать данные. По умолчанию, если вы не сопоставляете этот сигнал с Ведущим интерфейсом чтения AXI4, сгенерированное ядро IP HDL связывает rd_dready с логикой высоко.