Закодируйте двоичные данные с помощью конкатенированной схемы кодирования параллели

Сверточная подбиблиотека Выявления ошибок и Коррекции

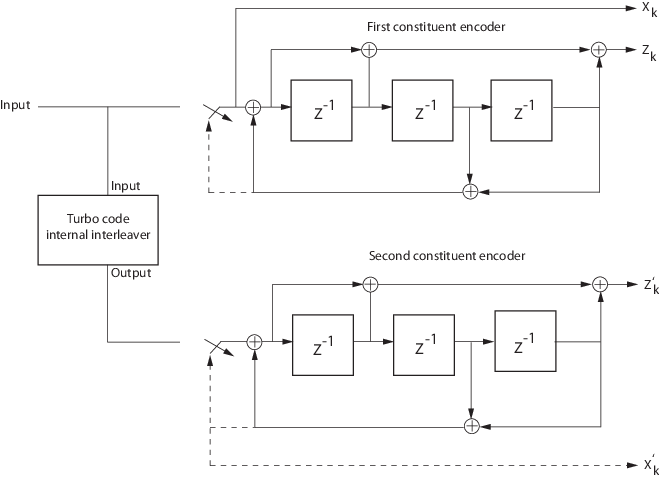

Блок Turbo Encoder кодирует сообщение двоичного входа использование параллельной схемы каскадного кодирования. Эта схема кодирования использует два идентичных сверточных энкодера и один внутренний interleaver. Каждый составляющий энкодер независимо отключен битами хвоста.

Предыдущая блок-схема иллюстрирует, что выход блока Turbo Encoder состоит из потоков систематических и битов четности первого энкодера, и только потоков бита четности второго энкодера.

Для уровня половина составляющего энкодера блок чередует эти три потока и мультиплексирует биты хвоста в конец закодированных потоков данных.

Для получения дополнительной информации о битах хвоста, смотрите оконечный Operation mode на странице с описанием блока Convolutional Encoder.

Этот блок принимает L-by-1 входной сигнал вектор-столбца и выводит M-by-1 сигнал вектор-столбца. Для данной решетки M и L связаны:

и

где

L = энкодер ввел длину

M = энкодер вывел длину

n = log2 (решетка. NumOutputSymbols), для уровня 1/2 решетка, n = 2

numTails = log2 (trellis.numStates) * n

Предыдущие схематические показы настройка энкодера для решетки, заданной значением по умолчанию параметра Trellis structure, poly2trellis(4, [13 15], 13). Для длины входного вектора 64 битов выход блока энкодера составляет 204 бита. Первые 192 бита соответствуют три 64 потока битов (систематичный (Xk) и четность (Zk) потоки битов от первого энкодера и четности (Z’k) поток битов второго энкодера), чередованный согласно Xk, Zk, Z’k. Последние 12 битов соответствуют битам хвоста от этих двух энкодеров, когда переключатели находятся в более низком положении, соответствующем пунктирным линиям. Первая группа шести битов (три систематических бита и три бита четности) является выходными битами хвоста от первого составляющего энкодера. Вторая группа шести битов (три систематических бита и три бита четности) является выходными битами хвоста от второго составляющего энкодера.

Из-за битов хвоста, выходной уровень энкодера кода немного меньше 1/3.

Структура решетки составляющего сверточного кода.

Задайте решетку как структуру MATLAB®, которая содержит описание решетки составляющего сверточного кода. В качестве альтернативы используйте poly2trellis функция, чтобы создать пользовательскую решетку с помощью продолжительности ограничения, (восьмеричный) генератор кода, и (восьмеричные) связи обратной связи.

Этот блок поддерживает только уровень 1 N решетками, где N является целым числом.

Структура по умолчанию является результатом poly2trellis (4, [13 15], 13).

Задайте источник interleaver индексов как Property или Input port.

Когда вы устанавливаете этот параметр на Property, блок использует параметр Interleaver indices, чтобы задать interleaver индексы.

Когда вы устанавливаете этот параметр на Input port, блок использует вторичный входной порт, IntrInd, чтобы задать interleaver индексы.

Задайте отображение что использование блока, чтобы переставить входные биты как вектор-столбец целых чисел. Значением по умолчанию является (64:-1:1).'. Это отображение является вектором с числом элементов, равным длине, L, входного сигнала. Каждый элемент должен быть целым числом между 1 и L без повторных значений.

Задайте, симулирует ли блок использование Code generation или Interpreted execution. Значением по умолчанию является Interpreted execution.

| Порт | Поддерживаемые типы данных |

|---|---|

| \in |

|

|

Для примера, который использует Турбо блоки Декодера Энкодера и Турбо, смотрите Параллельное Конкатенированное Сверточное Кодирование: пример Турбокодов.

[1] Berrou, C., А. Глэвиукс и П. Титимэджшима. "Около Шенноновского предельного кодирования с коррекцией ошибок и декодирования: турбокоды”, Продолжения Международной конференции IEEE по вопросам Коммуникаций, Женевы, Швейцария, май 1993, стр 1064–1070.

[2] Бенедетто, S., Г. Монторси, Д. Дивсэлэр и Ф. Поллара. “Модуль мягкого входа Мягкого Выхода Максимума следующей (MAP), чтобы декодировать параллельные и последовательные каскадные коды”, лаборатория реактивного движения отчет о выполнении работ TDA, издание 42-27, ноябрь 1996.

[3] Шлегель, Кристиан Б. и Ланс К. Перес. Решетчатое кодирование и турбокодирование, нажатие IEEE, 2004.

[4] 3GPP TS 36.212 v9.0.0, проект партнерства третьего поколения; сеть радиодоступа группы Технической характеристики; Развитый Универсальный Наземный Радио-доступ (к E-UTRA); Мультиплексирование и кодирование канала (релиз 9), 2009-12.