БПФ — оптимизированный для генерации HDL-кода с помощью минимальных аппаратных ресурсов

Устаревший

dspobs

Блок HDL Minimum Resource FFT будет удерживаться от использования в будущем релизе. Используйте Burst Radix 2 архитектура блока FFT HDL Optimized вместо этого.

Блок HDL Minimum Resource FFT реализует архитектуру БПФ, которая использует минимальные аппаратные ресурсы. Блок HDL Minimum Resource FFT поддерживает Основание 2 с алгоритмом децимации вовремя (DIT) для расчета БПФ. Смотрите блок FFT для получения дополнительной информации об этом алгоритме.

Результаты, возвращенные блоком HDL Minimum Resource FFT, поразрядно совместимы с результатами, возвращенными блоком FFT. Операция блока HDL Minimum Resource FFT отличается от блока FFT, из-за требований аппаратной реализации. Блок HDL Minimum Resource FFT:

Требует последовательного входа

Генерирует последовательный вывод

Действует в пакетном режиме I/O

Блок HDL Minimum Resource FFT обеспечивает сигналы квитирования поддерживать эти функции.

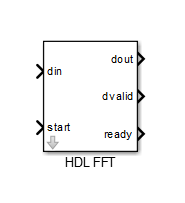

Как показано в следующем рисунке блок HDL Minimum Resource FFT имеет два входных порта и три выходных порта. Два из этих портов для ввода данных и выходных сигналов. Другие порты для управляющих сигналов.

Входные порты:

din: Сигнал входных данных. Требуется комплексный сигнал.

start: Булев управляющий сигнал. Когда этот сигнал является утверждаемой true (1), блок HDL Minimum Resource FFT инициирует обработку системы координат данных.

Выходные порты:

dout: Сигнал вывода данных. Основание 2 с алгоритмом DIT производит выход с линейным упорядоченным расположением.

dvalid: Булев управляющий сигнал. Блок HDL Minimum Resource FFT утверждает эту true (1) сигнала, когда пакет допустимых выходных данных доступен в dout порт.

ready: Булев управляющий сигнал. Блок HDL Minimum Resource FFT утверждает, что это сигнализирует, чтобы true (1) указала, что это готово обработать новый кадр.

Для эффективного аппаратного развертывания блока HDL Minimum Resource FFT синхронизация потоков входных и выходных данных блока должна быть рассмотрена тщательно. Следующий рисунок показывает временные зависимости между системными часами и start, ready, и dvalid сигналы.

Когда ready утверждается, start сигнал (активный высокий) инициировал блок. Высокий период цикла start сигнал не влияет на поведение блока.

Один такт после start инициируйте, блок начинает загружать данные и ready сигнал является deasserted. Во время интервала, когда блок загружает, обработка и вывод данных, ready является низким и start сигнал проигнорирован.

dvalid сигнал утверждается высоко для тактов N (где N является длиной БПФ) после того, как обработка завершена. ready утверждается снова после FFT N значений отосланы выходные параметры.

Выражение Tcycle обозначает общее количество тактов, требуемых блоком HDL Minimum Resource FFT завершать БПФ длины N. Tcycle определяется следующим образом:

Где N> 8

Tcycle = 3N/2-2 + log2(N)*(N/2+3);

Где N = 8

Tcycle = 3N/2-1 +log2(N)*(N/2+3);

Учитывая Tcycle, можно затем задать период между утверждениями БПФ Ресурса Минимума HDL start предупредите способом, что это подходит для вашего приложения. В “Используя Минимальный пример” БПФ HDL Ресурса, этот период вычислен и присвоен переменной startLen, можно следующим образом:

if (N<=8)

startLen = (ceil(Tcycle/N)+1)*N;

else

startLen = ceil(Tcycle/N)*N;

endВ модели в качестве примера, startLen определяет период Импульсного Генератора, который управляет блоком HDL Minimum Resource FFT start входной параметр. Эти значения вычисляются в функции инициализации модели (InitFcn), который задан в панели Callbacks Simulink® Model Explorer.

Блок HDL Minimum Resource FFT утверждает и deasserts ready и dvalid сигналы автоматически. Эти сигналы направляются к компонентам модели, которые пишут в и читают из блока HDL Minimum Resource FFT.

FFT Length

Значение по умолчанию: 8

Длина БПФ должна быть степенью 2 в области значений 23.. 216.

Rounding mode

Значение по умолчанию: Floor

Блок HDL Minimum Resource FFT поддерживает все режимы округления блока FFT. См. также раздел ссылки блока FFT.

Overflow mode

Значение по умолчанию: Saturate

Блок HDL Minimum Resource FFT поддерживает все режимы переполнения блока FFT. См. также раздел ссылки блока FFT.

Sine table

Значение по умолчанию: Same word length as input

Выберите, как вы задаете размер слова значений таблицы синуса. Дробная длина табличных значений синуса равна размеру слова минус один.

Когда вы выбираете Same word length as input, размер слова соответствия табличных значений синуса тот из входа с блоком.

Когда вы выбираете Specify word length, можно ввести размер слова табличных значений синуса, в битах, в поле Sine table word length. Табличные значения синуса не повинуются параметры Overflow mode и Rounding mode; они всегда насыщают и вокруг к Nearest.

Product output

Значение по умолчанию: Same as input

Используйте этот параметр, чтобы задать, как вы хотите назвать продукт выходным словом и дробными длинами:

Когда вы выбираете Same as input, эти характеристики совпадают с теми из входа с блоком.

Когда вы выбираете Binary point scaling, можно ввести размер слова и дробную длину продукта выход, в битах, в полях Product word length и Product fraction length.

Accumulator

Значение по умолчанию: Same as input

Используйте этот параметр, чтобы задать, как вы хотите определять слово аккумулятора и дробные длины:

Когда вы выбираете Same as product output, эти характеристики совпадают с теми из продукта выход.

Когда вы выбираете Same as input, эти характеристики совпадают с теми из входа с блоком.

Когда вы выбираете Binary point scaling, можно ввести размер слова и дробную длину аккумулятора, в битах, в полях Accumulator word length и Accumulator fraction length.

Output

Значение по умолчанию: Same as input

Выберите, как вы задаете выходной размер слова и дробную длину:

Когда вы выбираете Same as input, эти характеристики совпадают с теми из входа с блоком.

Когда вы выбираете Binary point scaling, можно ввести размер слова и дробная продолжительность выхода, в битах, в полях Output word length и Output fraction length.

Блок HDL FFT пропускает divide-two операцию на бабочке выходные параметры для сигналов фиксированной точки.

Чтобы начать с блоком HDL Minimum Resource FFT, запуститесь “Используя Минимальный пример” БПФ HDL Ресурса, который расположен в HDL Coder™ / библиотека Обработки сигналов в качестве примера.

Пример иллюстрирует использование блока HDL Minimum Resource FFT в симуляции. Модель включает буферизацию и управляющую логику, которая обрабатывает последовательный ввод и вывод. В примере комплексный исходный сигнал хранится как ряд выборок в FIFO. Выборки от FIFO обрабатываются последовательно блоком HDL Minimum Resource FFT, который испускает поток скалярных данных о БПФ.

Для сравнения тот же исходный сигнал также обрабатывается основанным на системе координат блоком FFT. Выходные системы координат от блока FFT буферизуются в FIFO и по сравнению с выходом блока HDL Minimum Resource FFT. Исследование результатов показывает выходные параметры, чтобы быть идентичным.

HDL Coder обеспечивает дополнительные параметры конфигурации, которые влияют на реализацию HDL и синтезируемую логику.

Этот блок имеет одну, архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. |

| InputPipeline | Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| OutputPipeline | Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |