Этот раздел относится к сгенерированным сущностям VHDL® или модулям Verilog® в общем как “сущности”.

mapping file является текстовым файлом отчета, сгенерированным makehdl. Сопоставляющие файлы сгенерированы как помощь в прослеживании сгенерированных сущностей HDL к соответствующим системам в модели.

Файл отображения показывает отношение между системами в модели и сущностях VHDL или модулях Verilog, которые были сгенерированы от них. Запись файла отображения имеет форму

path --> HDL_name

path полный путь к системе в модели и HDL_name имя модуля сущности или Verilog VHDL, который был сгенерирован от той системы. Файл отображения содержит одну запись на строку.В простых случаях файл отображения может содержать только одну запись. Например, symmetric_fir подсистема sfir_fixed модель генерирует следующий файл отображения:

sfir_fixed/symmetric_fir --> symmetric_fir

Сопоставляющие файлы более полезны, когда HDL-код сгенерирован от сложных моделей, где несколько подсистем генерируют многие сущности, и в случаях, где конфликты между тождественно именованными подсистемами разрешены HDL Coder™.

Если имя подсистемы уникально в модели, HDL Coder просто использует имя подсистемы в качестве сгенерированного имени сущности. Где с тождественно именованными подсистемами сталкиваются, кодер пытается разрешить конфликт путем добавления постфиксной строки (по умолчанию, '_entity') к конфликтной подсистеме. Если впоследствии сгенерированный конфликт имен сущности в свою очередь с этим именем, инкрементные цифры (1,2,3... ) добавлены.n

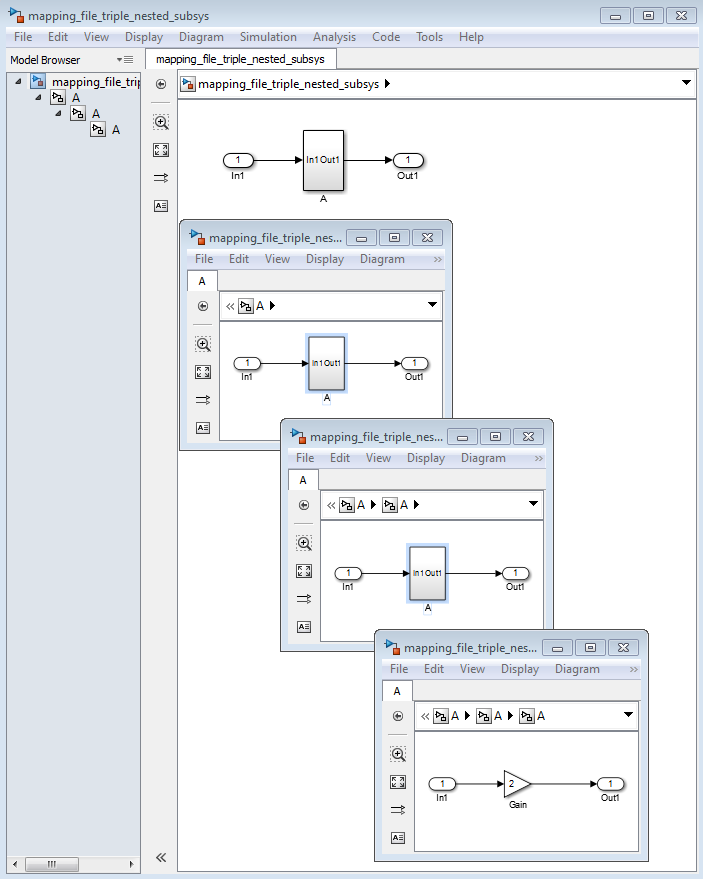

Как пример, считайте модель показанной в следующем рисунке. Модель верхнего уровня содержит подсистемы под названием A вложенный к трем уровням.

Когда код сгенерирован для подсистемы верхнего уровня A, makehdl прокладывает себе путь от самого глубокого уровня иерархии модели, генерируя уникальные имена сущности для каждой подсистемы.

makehdl('mapping_file_triple_nested_subsys/A')

### Working on mapping_file_triple_nested_subsys/A/A/A as A_entity1.vhd

### Working on mapping_file_triple_nested_subsys/A/A as A_entity2.vhd

### Working on mapping_file_triple_nested_subsys/A as A.vhd

### HDL Code Generation Complete.

Следующий пример перечисляет содержимое результирующего файла отображения.

mapping_file_triple_nested_subsys/A/A/A --> A_entity1 mapping_file_triple_nested_subsys/A/A --> A_entity2 mapping_file_triple_nested_subsys/A --> A

Учитывая эту информацию, можно проследить сгенерированную сущность до ее соответствующей подсистемы при помощи open_system команда, например:

open_system('mapping_file_triple_nested_subsys/A/A')

Каждый сгенерированный файл сущности также содержит путь для своей соответствующей подсистемы в комментариях заголовка наверху файла, как в следующей выборке кода.

-- Module: A_entity2 -- Simulink Path: mapping_file_triple_nested_subsys/A -- Hierarchy Level: 0