Можно использовать возможность генерации теста, предусмотренную Simulink® Design Verifier™, чтобы сгенерировать тесты для исполняемой спецификации, модель, используемая в генерации производственного кода или любой другой временной модели, созданной во время фазы моделирования. Можно использовать сгенерированные тесты, чтобы стимулировать исполняемую спецификацию или другой этап рабочего процесса Модельно-ориентированного проектирования.

Можно использовать возможность поиска ошибок проектирования, предусмотренную Simulink Design Verifier, чтобы обнаружить мертвую логику, переполнение данных целочисленной или фиксированной точки, деление на нуль и нарушения заданных промежуточных минимальных и максимальных значений.

Варианты использования инструмента обеспечиваются в документе Пакета квалификации инструмента (TQP) ISO 26262 Simulink Design Verifier. Варианты использования не только допустимы для ISO 26262, но и распознаны за все стандарты соответственно.

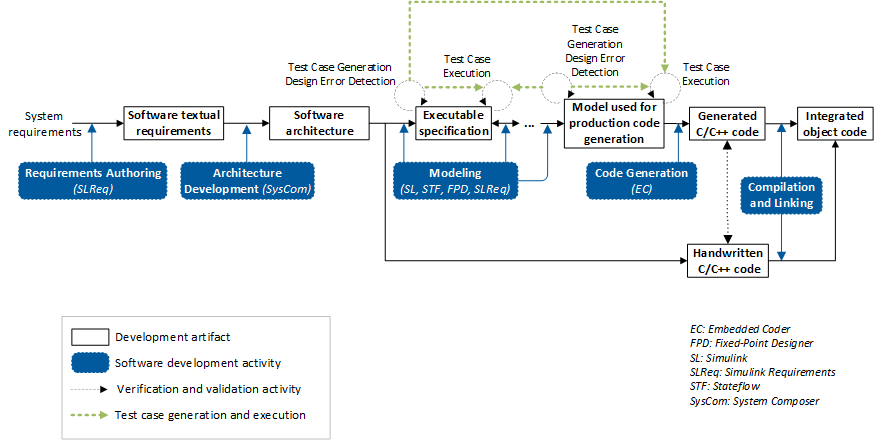

Этот рисунок иллюстрирует интегрирование генерации теста и поиска ошибок проектирования с помощью Simulink Design Verifier в качестве части рабочего процесса Модельно-ориентированного проектирования. Твердые стрелки в фигуре указывают на последовательность действий разработки программного обеспечения. Модели, используемые в генерации производственного кода, могут содержать рукописный исходный код. Например, код С содержится в пользовательских S-функциях. Этот вариант использования смешанного кода показан стрелкой между рукописным кодом C/C++ и моделью, используемой в полях генерации производственного кода.

Simulink Design Verifier в рабочем процессе модельно-ориентированного проектирования