Можно сгенерировать допускающее повторное использование ядро IP HDL для любого, поддержал устройство Altera® FPGA или Xilinx®. Рабочий процесс представляет отчет ядра IP, который отображает целевую интерфейсную настройку и настройки кодера, которые вы задаете. Смотрите Пользовательскую Генерацию Ядра IP.

Можно опционально создать собственные исходные проекты и интегрировать сгенерированное ядро IP в исходный проект. Рабочий процесс не требует программного обеспечения Embedded Coder®, потому что вы не должны генерировать встроенный код, который запущен на процессоре. Это означает, что рабочий процесс не имеет задачи Generate Software Interface Model.

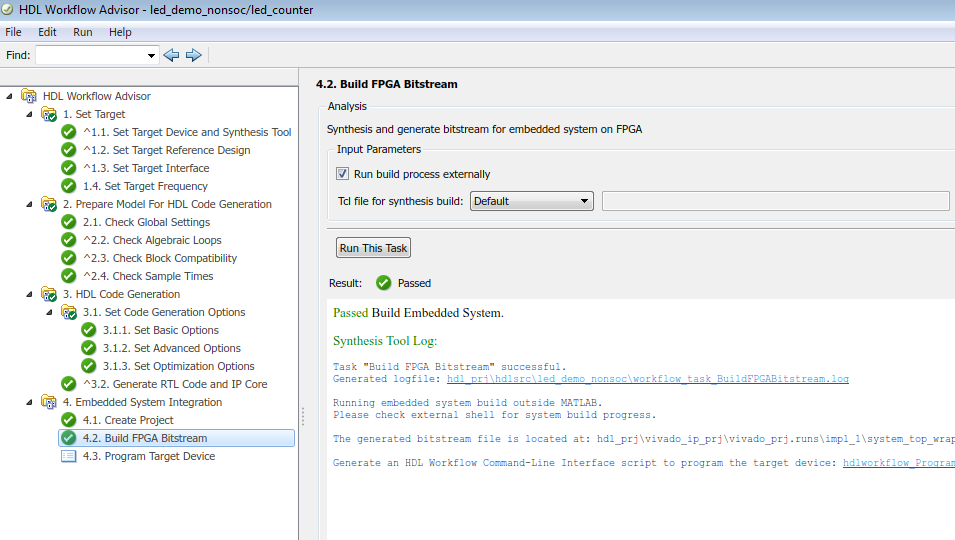

Рабочий процесс для плат FPGA имеет эти функции:

Задача Set Target Reference Design. Заполняет исходный проект, его версию инструмента и параметры, которые вы задаете.

Задача Set Target Interface. Сопоставьте свои порты DUT с интерфейсами на целевой платформе.

Задача Set Target Frequency. Задает Target Frequency (MHz), чтобы изменить модуль тактовой синхронизации в исходном проекте, чтобы произвести сигнал часов с той частотой.

Задача Generate RTL Code and IP Core. Генерирует допускающее повторное использование и ядро IP с обеспечением совместного доступа. Ядро IP группирует код RTL, заголовочный файл C и файлы определения ядра IP.

Задача Create Project. Создает проект для интеграции ядра IP в предопределенные исходные проекты.

Можно сгенерировать ядро IP с дополнительным AXI4 или интерфейсом AXI4-Lite.

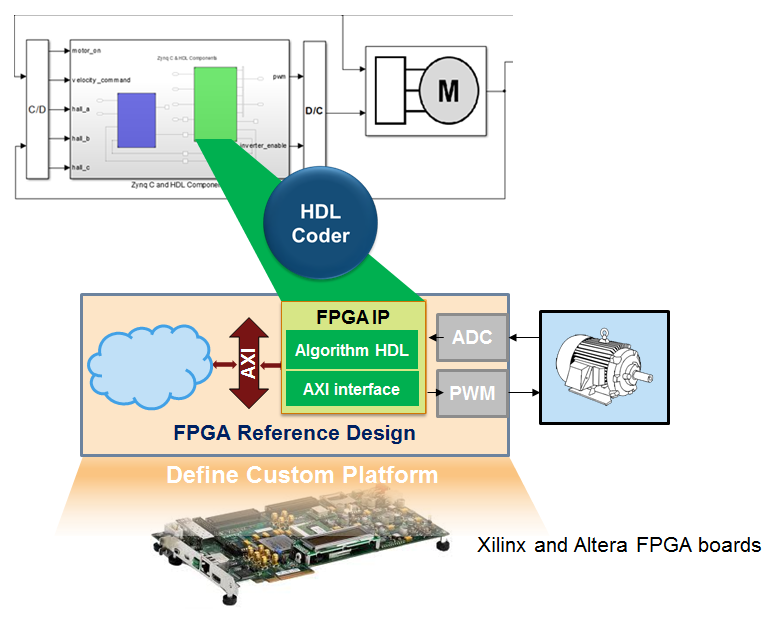

Этот рисунок показывает, как HDL Coder™ генерирует ядро IP с интерфейсом AXI4 и интегрирует ядро IP в исходный проект FPGA. Смотрите система регистрации Исходного проекта и Совет.

Используйте сгенерированный интерфейс AXI4-Lite HDL Coder, чтобы соединить ядро IP с AXI4 или AXI4-облегченным Ведущим устройством, таким как:

Процессор MicroBlaze.

Процессор Nios II.

Конечная точка PCIe, которая связывает с внешним процессором.

Ведущее устройство JTAG.

Когда вы соединяете ядро IP HDL с процессором, таким как MicroBlaze, необходимо интегрировать рукописный код С, чтобы работать на процессоре. Сгенерированный отчет ядра IP отображает информацию об отображении адресов регистра. Чтобы найти смещения регистра на пробеле регистра ядра IP, используйте эту информацию об отображении. Чтобы получить адрес памяти каждого регистра, добавьте смещение регистра в базовый адрес, который вы задаете в своем исходном проекте. Можно также найти смещения регистра в заголовочном файле C в сгенерированной папке ядра IP.

В функции определения исходного проекта можно создать собственные исходные проекты без ведомого интерфейса AXI4. См. также addAXI4SlaveInterface.

Когда создание пользовательского исходного проекта, чтобы предназначаться для автономной платы FPGA, использует EmbeddedCoderSupportPackage метод hdlcoder.ReferenceDesign класс:

hRD.EmbeddedCoderSupportPackage = hdlcoder.EmbeddedCoderSupportPackage.None;

EmbeddedCoderSupportPackage.HDL Coder поддерживает эти платы FPGA с IP Core Generation рабочий процесс:

Xilinx Kintex-7 KC705 development board

Arrow DECA MAX 10 FPGA evaluation kit

Используя эти платы, можно интегрировать сгенерированное ядро IP в default system исходный проект. По умолчанию этот исходный проект не имеет ведомого интерфейса AXI4. Опционально, можно добавить интерфейс в функции определения исходного проекта.