Этот пример сначала выбирает оптимизированную скоростью реализацию блока Sum для простой модели, которая вычисляет векторную сумму. Это затем исследует сгенерированную модель и определяет местоположение числовых изменений, введенных оптимизацией.

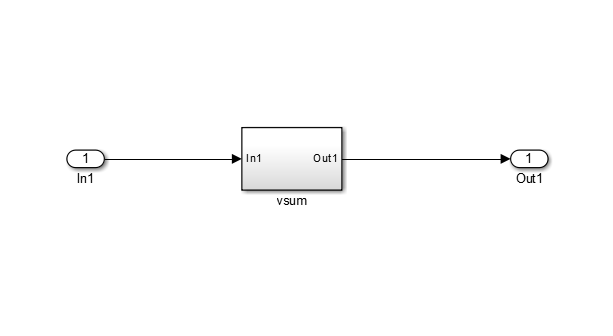

Модель, simplevectorsum, состоит из Subsystem, vsum, управляемый векторным входом ширины 10, со скалярным выходом. Следующий рисунок показывает корневой уровень модели.

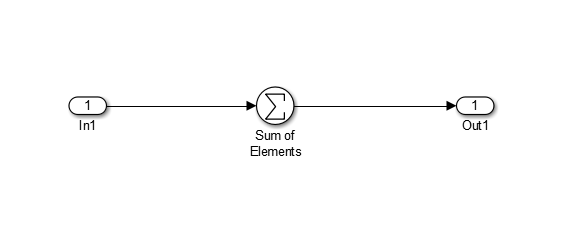

Устройством под тестом является vsum подсистема, показанная в следующем рисунке. Подсистема содержит блок Sum, сконфигурированный для векторного суммирования.

Модель сконфигурирована, чтобы использовать Tree реализация при генерации HDL-кода для блока Sum в vsum подсистема. Эта реализация, оптимизированная в течение минимальной задержки, генерирует структуру древовидной формы сумматоров для блока Sum.

Выбрать реализацию не по умолчанию для отдельного блока:

Щелкните правой кнопкой по блоку и выберите HDL Code> HDL Block Properties .

В диалоговом окне HDL Properties выберите желаемую реализацию из меню Architecture.

Нажмите Apply и закройте диалоговое окно.

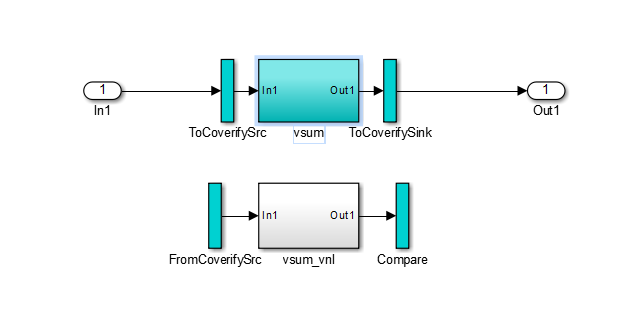

После генерации кода можно просмотреть модель валидации, gm_simplevectorsum_tree_vnl.

vsum подсистема была подсвечена в голубом цвете. Это выделение указывает, что подсистема отличается по некоторому уважению от vsum подсистема исходной модели.

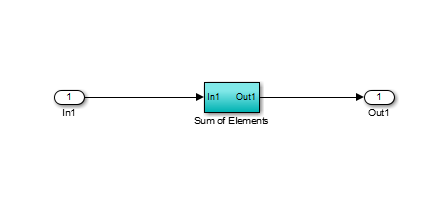

Следующий рисунок показывает vsum подсистема в сгенерированной модели. Заметьте, что блок Sum теперь реализован как подсистема, которая также кажется подсвеченной.

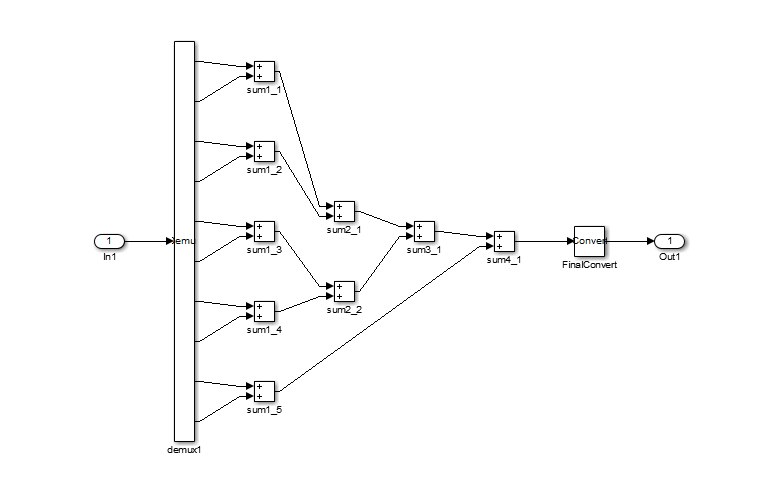

Следующий рисунок показывает внутреннюю структуру подсистемы Суммы.

Сгенерированная модель реализует векторную сумму как дерево сумматоров (Блоки суммы). Векторный входной сигнал демультиплексируется и соединяется, как пять пар операндов, к пяти крайним левым сумматорам. Ширины сумматора выходные параметры увеличиваются слева направо, как требуется чтобы избежать переполнения в вычислительных промежуточных результатах.