По умолчанию кодер представляет константы как скаляры или агрегируется в зависимости от размера и типа данных. Кодер представляет значения, которые меньше 232 – 1 как целые числа и значения, больше, чем или равны 232 – 1, как агрегируется. Следующие объявления константы VHDL являются примерами объявлений, сгенерированных по умолчанию для значений меньше чем 32 бита:

CONSTANT coeff1: signed(15 DOWNTO 0) := to_signed(-60, 16); -- sfix16_En16 CONSTANT coeff2: signed(15 DOWNTO 0) := to_signed(-178, 16); -- sfix16_En16

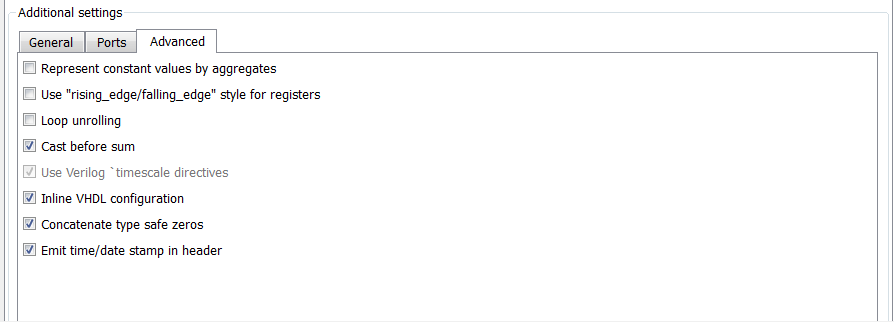

Если вы предпочитаете, чтобы постоянные значения были представлены, как агрегируется, установите Represent constant values by aggregates можно следующим образом:

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку Advanced.

Выберите Represent constant values by aggregates, как показано следующая фигура.

Предыдущие объявления константы теперь появились бы следующими:

CONSTANT coeff1: signed(15 DOWNTO 0) := (5 DOWNTO 3 => '0',1 DOWNTO 0 => '0,OTHERS =>'1'); CONSTANT coeff2: signed(15 DOWNTO 0) := (7 => '0',5 DOWNTO 4 => '0',0 => '0',OTHERS =>'1');

Альтернатива командной строки: используйте generatehdl функция со свойством UseAggregatesForConst представлять константы в HDL-коде, как агрегируется.

По умолчанию кодер поддерживает циклы VHDL. Однако некоторые инструменты EDA не поддерживают их. Если вы используете такой инструмент наряду с VHDL, можно развернуть и удалить FOR и GENERATE циклы из сгенерированного кода VHDL. Код Verilog уже развернут.

Развернуть и удалить FOR и GENERATE циклы,

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку Advanced. Панель Advanced появляется.

Выберите Loop unrolling как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством LoopUnrolling развернуть и удалить циклы из сгенерированного кода VHDL.

Кодер может сгенерировать два стиля кода VHDL для проверки возрастающие ребра, когда фильтр работает с регистрами. По умолчанию сгенерированный код проверяет на событие часов, как показано в ELSIF оператор следующего блока процесса VHDL.

Delay_Pipeline_Process : PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

delay_pipeline(0 TO 50) <= (OTHERS => (OTHERS => '0'));

ELSEIF clk'event AND clk = '1' THEN

IF clk_enable = '1' THEN

delay_pipeline(0) <= signed(filter_in);

delay_pipeline(1 TO 50) <= delay_pipeline(0 TO 49);

END IF;

END IF;

END PROCESS Delay_Pipeline_Process ;

Если вы предпочитаете, кодер может произвести код VHDL, который применяет VHDL rising_edge функцию вместо этого. Например, ELSIF оператор в предыдущем блоке процесса был бы заменен следующим оператором:

ELSIF rising_edge(clk) THEN

Использовать rising_edge функция,

Нажмите Global Settings в диалоговом окне Generate HDL.

Выберите вкладку Advanced. Панель Advanced появляется.

Выберите Use 'rising_edge' for registers, как показано в следующем диалоговом окне.

Альтернатива командной строки: используйте generatehdl функция со свойством UseRisingEdge использовать VHDL rising_edge функционируйте, чтобы проверять на возрастающие ребра во время операций регистра.

Настройки VHDL могут быть или встроенными с остальной частью кода VHDL для сущности или внешними в отдельных исходных файлах VHDL. По умолчанию кодер включает настройки для фильтра в рамках сгенерированного кода VHDL. Если вы создаете свои собственные конфигурационные файлы VHDL, подавляете генерацию встроенных настроек.

Подавить генерацию встроенных настроек,

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку Advanced. Панель Advanced появляется.

Очистите Inline VHDL configuration как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством InlineConfigurations подавить генерацию встроенных настроек.

В VHDL конкатенация нулей может быть представлена в двух формах синтаксиса. Одна форма, '0' & '0', безопасно с точки зрения типов. Этот синтаксис является значением по умолчанию. Альтернативный синтаксис, "000000...", может быть легче читать и более компактен, но может привести к неоднозначным типам.

Использовать синтаксис "000000..."для конкатенированных нулей,

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку Advanced. Панель Advanced появляется.

Очистите Concatenate type safe zeros как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством SafeZeroConcat использовать синтаксис "000000...", для конкатенированных нулей.

По умолчанию сгенерированный HDL-код работает с входными данными с помощью типов данных, как задано созданием фильтра, и затем преобразует результат в заданный тип результата.

Типичные процессоры DSP вводят входные данные броска к типу результата прежде, чем работать с данными. В зависимости от операции результаты могут отличаться. Если вы хотите, чтобы сгенерированный HDL-код обработал результат, вводящий таким образом, используйте опцию Cast before sum можно следующим образом:

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку Advanced. Панель Advanced появляется.

Выберите Cast before sum как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством CastBeforeSum чтобы бросить входные значения к результату вводят для операций сложения и операций вычитания.

Опция Cast before sum связана с установкой Filter Designer для опции квантования Cast signals before sum можно следующим образом:

Некоторые типы объекта фильтра не имеют свойства Cast signals before sum. Для таких объектов фильтра Cast before sum эффективно выключен, когда HDL-код сгенерирован; это не относится к фильтру.

Где объект фильтра действительно имеет свойство Cast signals before sum, кодер по умолчанию следует за установкой Cast signals before sum в объекте фильтра. Эта установка отображается в пользовательском интерфейсе. Если вы изменяете настройки Cast signals before sum, кодер обновляет установку Cast before sum.

Однако явным образом установкой Cast before sum, можно заменить установку Cast signals before sum, переданную в от Filter Designer.

В Verilog кодер генерирует директивы масштаба времени (ˋtimescale) по умолчанию. Эта директива компилятора обеспечивает способ задать различные значения задержки для нескольких модулей в файле Verilog.

Подавить использование ˋtimescale директивы,

Выберите вкладку Global Settings на диалоговом окне Generate HDL.

Выберите вкладку Advanced. Панель Advanced появляется.

Очистите Use Verilog ˋtimescale directives как показано в следующем рисунке.

Альтернатива командной строки: используйте generatehdl функция со свойством UseVerilogTimescale подавить использование директив масштаба времени.

Кодер поддерживает комплексные коэффициенты и комплексные входные сигналы.

Чтобы сгенерировать порты и пути прохождения сигнала для действительных и мнимых компонентов комплексного входного сигнала, установите Input complexity на Complex. Настройкой по умолчанию для Input complexity является Real, отключение генерации портов для комплексных входных данных.

Соответствующим свойством командной строки является InputComplex. По умолчанию, InputComplex установлен в 'off', отключение генерации портов для комплексных входных данных. Чтобы включить генерацию портов для комплексных входных данных, установите InputComplex к 'on', как в следующем примере кода:

filt = design(fdesign.lowpass,'equiripple','Filterstructure','dffir','SystemObject',true); generatehdl(filt,numerictype(1,16,15),'InputComplex','on')

Следующая выборка VHDL кода показывает определение сущности, сгенерированное предыдущими командами:

ENTITY firfilt IS

PORT( clk : IN std_logic;

clk_enable : IN std_logic;

reset : IN std_logic;

filter_in_re : IN std_logic_vector(15 DOWNTO 0); -- sfix16_En15

filter_in_im : IN std_logic_vector(15 DOWNTO 0); -- sfix16_En15

filter_out_re : OUT std_logic_vector(37 DOWNTO 0); -- sfix38_En31

filter_out_im : OUT std_logic_vector(37 DOWNTO 0) -- sfix38_En31

);

END firfilt;

В выборке кода имена порта, сгенерированные для действительных компонентов комплексных сигналов, имеют постфиксный '_re' по умолчанию, и имена порта, сгенерированные для мнимых компонентов комплексных сигналов, имеют постфиксный '_im' по умолчанию.

Два свойства генерации кода позволяют вам настроить соглашения о присвоении имен для действительных и мнимых компонентов комплексных сигналов в сгенерированном HDL-коде. Эти свойства:

Опция Complex real part postfix (соответствующий ComplexRealPostfix свойство командной строки), задает вектор символов, который будет добавлен к именам, сгенерированным для действительной части комплексных сигналов. Постфиксом по умолчанию является '_re'.

Опция Complex imaginary part postfix (соответствующий ComplexImagPostfix свойство командной строки), задает вектор символов, который будет добавлен к именам, сгенерированным для мнимой части комплексных сигналов. Постфиксом по умолчанию является '_im'.