FPGA в цикле (FIL) симуляция предусматривает возможность использовать Simulink® или MATLAB для тестирования проектов в действительном оборудовании для любого существующего HDL-кода. HDL-код может быть или вручную записан или программное обеспечение, сгенерированное от подсистемы модели.

У вас должен быть HDL-код, чтобы выполнить симуляцию FIL. Существует два рабочих процесса FIL:

У вас есть существующий HDL-код (мастер FIL).

Мастер FIL использует любой синтезируемый HDL-код включая код, автоматически сгенерированный из моделей Simulink программным обеспечением HDL Coder™

У вас есть код MATLAB или модель Simulink и лицензия HDL Coder (HDL Workflow Advisor).

Когда вы используете FIL в Советнике по вопросам Рабочего процесса, HDL Coder использует загруженный проект, чтобы создать HDL-код.

Неважно, который рабочий процесс вы выбираете, FIL выполняет следующие процессы, когда это создает блок или Систему object™:

Генерирует блок FIL или Системный объект FIL, который представляет HDL-код

Обеспечивает синтез, логическое отображение, место-и-маршрут (PAR), программируя генерацию файла и коммуникационный канал.

Загружает проект на FPGA

Все эти возможности спроектированы для конкретной платы и адаптированы в соответствии с вашим кодом RTL.

Как часть симуляции FIL, блока или Системного объекта и вашей модели или приложения:

Данные о передачах из Simulink или MATLAB к FPGA

Получает данные из FPGA

Осуществляет проект в действительной среде

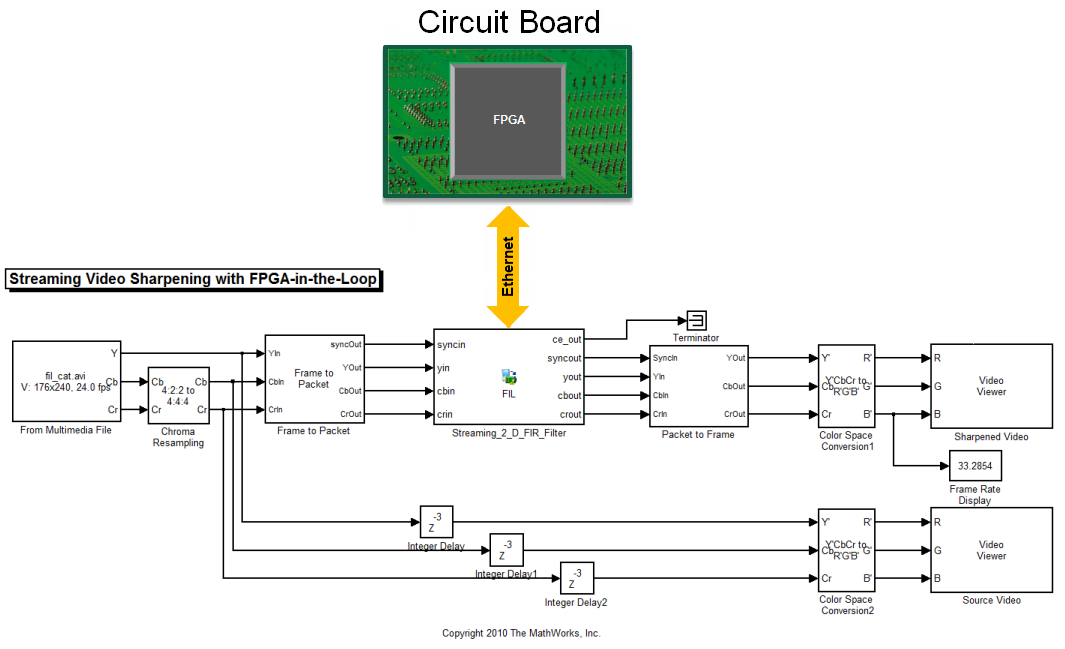

FIL Communications. Следующая фигура демонстрирует, как HDL Verifier™ передает между Simulink и использованием платы FPGA симуляцию FIL.

HDL Verifier принимает, что существует только один кабель загрузки, соединенный с хостом - компьютером, и что программное обеспечение для программирования FPGA может автоматически обнаружить эту связь. В противном случае используйте программное обеспечение для программирования FPGA, чтобы программировать ваш FPGA с правильными опциями.

Представление уровня системы. Все DUT I/Os направляются к Simulink через коммуникационную логику FIL.

FIL обеспечивает канал связи для отправки и получения данных между Simulink и FPGA. Этот канал может быть JTAG, Ethernet или связью PCI Express®. Связь между Simulink и FPGA строго синхронизируется, чтобы обеспечить надежную среду верификации.

Чтобы создать FIL программирование файла, программное обеспечение выполняет следующие задачи:

Генерирует HDL-код для заданного DUT и создает проект ISE.

Наряду с вашим программным обеспечением проекта FPGA, синтезирует, сопоставляет, помещает и направляет и создает файл программирования для FPGA.

Загружает файл программирования на FPGA на макетной плате посредством нормальной связи настройки. Как правило, та связь является последовательной линией по USB-кабелю (см. руководство участника форума для того, как установить эту связь).

Для блоков симуляции FIL, нажатие по Load на маске блока FIL инициирует загрузку файла программирования.

Для Системных объектов симуляции FIL, выпуская programFPGA метод инициирует загрузку файла программирования.

Для симуляции FIL у вас должны быть следующие элементы или готовая информация:

Для мастера FIL:

Обеспечьте HDL-код (или вручную записанный или сгенерированное программное обеспечение) для проекта, который вы намереваетесь протестировать.

Выберите файлы HDL и задайте имя модуля верхнего уровня.

Рассмотрите параметры порта и убедитесь, что мастер FIL идентифицировал сигналы ввода и вывода и размеры сигнала как ожидалось.

Если вы используете Simulink, предоставьте модель Simulink, готовую получить сгенерированный блок FIL.

Для HDL Workflow Advisor:

Можно сгенерировать код и запустить FIL из любой подходящей модели Simulink. Следуйте за рабочим процессом для FPGA-in-the-Loop. См. Симуляцию FIL с HDL Workflow Advisor для Simulink. Для кода MATLAB смотрите рабочий процесс, описанный в Симуляции FIL с HDL Workflow Advisor для MATLAB.