Если у вас есть большая модель, которая замедляет ваш анализ или имеет недостижимые цели, можно хотеть анализировать атомарные подсистемы или Stateflow® атомарные подграфики с помощью Simulink® Design Verifier™. Этот метод позволяет вам реализовывать подход снизу вверх к анализу большой модели, как описано в Подходе снизу вверх к Анализу модели.

Когда вы анализируете подсистему или атомарный подграфик, программное обеспечение:

Извлекает подсистему или подграфик в новую модель.

При необходимости добавляют блоки к недавно созданной модели, которые реплицируют контекст выполнения подсистемы или подграфика в его родительской модели.

Анализирует извлеченную модель и приводит к результатам.

Программное обеспечение Simulink Design Verifier может только анализировать атомарные подсистемы и атомарные подграфики.

Для получения дополнительной информации об анализе подсистем, смотрите, Генерируют Тесты для Подсистемы.

Для получения дополнительной информации об анализе атомарных подграфиков, смотрите, Анализируют Stateflow Атомарный Подграфик.

sldvextract функция позволяет вам извлекать подсистемы и атомарные подграфики для верификации компонента. Путем извлечения подсистемы или атомарного подграфика, можно проверить компонент в изоляции от остальной части системы, позволив вам протестировать алгоритм компонента. Для получения дополнительной информации смотрите то, Что Верификация Компонента? и Функции для Верификации Компонента.

Когда вы анализируете подсистему или атомарный подграфик, Simulink Design Verifier создает новую модель, которая содержит подсистему или атомарный подграфик и любые порты ввода и вывода, которые соответствуют портам, соединенным с исходной подсистемой. Программное обеспечение присваивает следующие свойства портам в новой модели, как определено путем компиляции исходной модели:

Типы данных

Частоты дискретизации

Размерности сигнала

Названия программного обеспечения новая модель subsystem_name, где subsystem_name имя подсистемы.

Следующие разделы обеспечивают примеры того, как Simulink Design Verifier извлекает и анализирует подсистемы.

data store является репозиторием, к которому можно записать данные, и от которого можно считать данные, не имея необходимость соединять сигнал ввода или вывода непосредственно с хранилищем данных.

Вы создаете хранилище данных с помощью блока Data Store Memory или Simulink.Signal объект. Блок Data Store Memory или Simulink.Signal объект представляет хранилище данных и задает его свойства. Каждое хранилище данных должно иметь уникальное имя.

Когда вы анализируете подсистему, которая считывает данные из хранилища данных, к которому получают доступ вне подсистемы, анализа:

Добавляет блок Data Store Memory к новой модели.

Добавляет входной порт, который пишет в хранилище данных. Поскольку вход пишет в хранилище данных, данные могут иметь любые значения (в заданном типе данных) в целях анализа Simulink Design Verifier.

Если хранилище данных задает минимальные и максимальные значения, те значения присвоены новому входному порту.

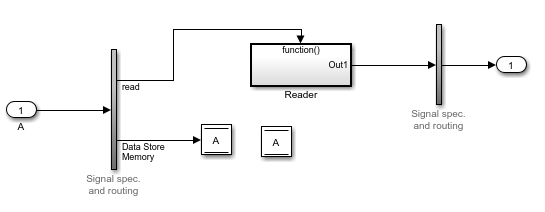

Следующий пример анализирует подсистему в sl_subsys_fcncall8 модель в качестве примера:

Откройте sl_subsys_fcncall8 модель в качестве примера:

Эта модель задает хранилище данных A, из которого Читатель атомарной подсистемы считывает данные с помощью блока Data Store Read.

Щелкните правой кнопкой по подсистеме Читателя и выберите Design Verifier> Generate Tests for Subsystem.

Логарифмическое окно Simulink Design Verifier показывает, что программное обеспечение извлекает подсистему в новую модель под названием Reader, анализирует извлеченную модель и предлагает вам, выбор которых заканчивается, чтобы произвести.

Откройте новый Reader модель, что программное обеспечение создается в <current_folder>\sldv_output\Reader

Новый блок Inport записи в хранилище данных, которое используется Читателем подсистемы в новой модели.

function-call subsystem является инициированной подсистемой, выполнение которой определяется логикой, внутренней к S-функции MEX C вместо значением сигнала. Подсистемы вызова функций являются всегда атомарными.

Для получения дополнительной информации смотрите Подсистемы вызова функций Реализации с S-функциями (Simulink).

Когда вы анализируете модель с подсистемой вызова функций, Simulink Design Verifier создает новую модель с блоком Inport, который подражает триггеру и копии подсистемы. Программное обеспечение затем анализирует новую модель.

Следующий пример анализирует подсистему вызова функций в sl_subsys_fcncall2 модель:

Откройте sl_subsys_fcncall2 модель в качестве примера:

Эта модель содержит диаграмму Stateflow под названием График, который инициировал подсистему вызова функций f.

Щелкните правой кнопкой по f подсистеме и выберите Design Verifier> Generate Tests for Subsystem.

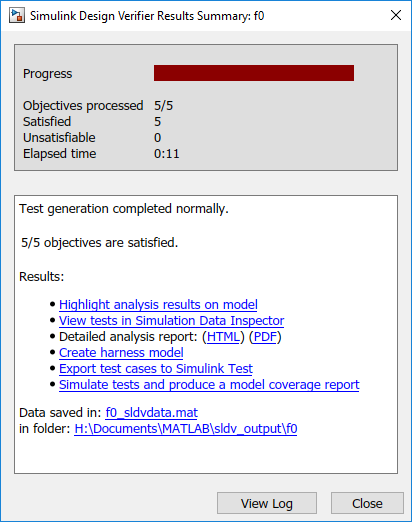

Программное обеспечение извлекает подсистему в новую модель под названием f0, анализирует извлеченную модель и приводит к результатам.

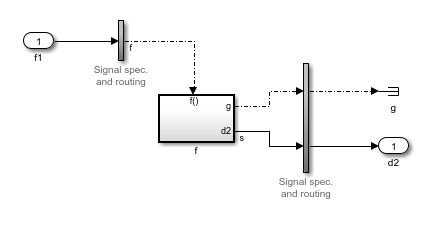

Откройте f0 модель, что программное обеспечение создается в <current_folder>\sldv_output\f0

Блок Inport и новый блок подсистемы подражают триггеру для подсистемы вызова функций f в новом f0 модель.