Логические блоки Simulink® Design Verifier™consider как закорачивающий во время анализа.

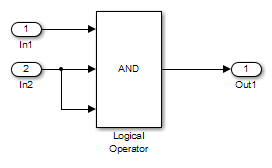

Рассмотрите следующую модель в качестве примера с набором параметра Model coverage objectives к Condition Decision. В этом случае, когда один только предыдущий вход определяет блок выход, анализ игнорирует любые входные параметры оставшегося блока. Если первый вход с блоком Logical Operator, параметр Operator которого задает AND является ложным, анализ игнорирует значения других входных параметров.

Когда Simulink Design Verifier анализирует эту модель для Decision Coverage Условия, анализ может только удовлетворить пяти из шести целей для входных параметров блока Logical Operator. Программное обеспечение не может сгенерировать тест, когда третий вход с блоком Logical Operator является ложным. Если второй вход является ложным, третий вход является ложным, но программное обеспечение игнорирует третий вход из-за замыкания накоротко. Если второй вход верен, третий вход никогда не является ложным.