Вычисляет быстрое преобразование Фурье (FFT) для пропускной способности передачи стандарта LTE 15 МГц

Wireless HDL Toolbox / Модуляция

Блок FFT 1536 спроектирован, чтобы поддержать пропускную способность передачи стандарта LTE 15 МГц. Этот блок используется в блочной операции LTE OFDM Demodulator. Блок принимает входные данные, наряду с допустимым управляющим сигналом и выходными параметрами, передающими данные потоком с samplecontrol шина.

Блок обеспечивает архитектуру, подходящую для аппаратного развертывания и генерации HDL-кода.

data — Входные данныеВходные данные в виде скаляра действительных или комплексных чисел.

double и single входные данные позволены для симуляции, но не для генерации HDL-кода.

Чем больше дробные биты, которые вы обеспечиваете во входном размере слова, тем лучше точность вы получаете в выходе.

Типы данных: double | single | int8 | int16 | int32 | fixed point

Поддержка комплексного числа: Да

valid — Указывает на допустимые входные данныеBoolean скалярУказывает, допустимы ли входные данные. Когда входом valid является 1 (TRUE), блок получает значение на порте входа data. Когда входом valid является 0 (FALSE), блок игнорирует выборки входа data.

Типы данных: Boolean

reset — Сбросьте управляющий сигналBoolean скалярКогда этим значением является 1 (TRUE), блок останавливает текущее вычисление и очищает все внутренние состояния.

Чтобы включить этот порт, выберите параметр Enable reset input port.

Типы данных: Boolean

data — Выходные данные канала частотыВыходные данные канала частоты, возвращенные как скаляр действительных или комплексных чисел.

Когда вход имеет fixed point тип данных, тип выходных данных совпадает с типом входных данных. Когда вход имеет целочисленный тип, тип выходных данных имеет fixed point ввод.

Типы данных: double | single | int8 | int16 | int32 | fixed point

Поддержка комплексного числа: Да

ctrl — Управляющие сигналы сопроводительный демонстрационный потокsamplecontrol шинаУправляющие сигналы, сопровождающие демонстрационный поток, возвращенный как samplecontrol шина. Шина включает startконец, и valid управляющие сигналы, которые указывают на контуры системы координат и валидность выборок.

start — Указывает на запуск выходной системы координат

end — Указывает на конец выходной системы координат

valid — Указывает, что данные по порту выхода data допустимы

Типы данных: bus

Complex multiplication — Реализация HDLUse 3 multipliers and 5 adders (значение по умолчанию) | Use 4 multipliers and 2 addersЗадает комплексный тип множителя для реализации HDL. Каждое умножение реализовано любой с Use 3 multipliers and 5 adders или с Use 4 multipliers and 2 adders. Скорость реализации зависит от инструмента синтеза и целевого устройства, которое вы используете.

Rounding method — Режим Rounding для внутренних вычислений фиксированной точкиFloor (значение по умолчанию) | Ceiling | Convergent | Nearest | Round | ZeroЗадает тип округления метода для внутренних вычислений фиксированной точки. Для получения дополнительной информации об округлении методов, смотрите Округление Режимов (DSP System Toolbox). Когда вход является любым целым числом или типом данных с фиксированной точкой, этот блок использует вычисления с фиксированной точкой во внутренних вычислениях. Этот параметр не применяется, когда входными данными является single или double.

Normalize butterfly output — Выведите нормализациюoff (значение по умолчанию) | onКогда вы выбираете этот параметр, блок делит выход на 1 536. Эта опция полезна, когда это необходимо, выход блока, чтобы остаться в той же амплитудной области значений как ее вход. Вы требуете этой опции, когда вход имеет fixed point ввод.

Когда вы выбираете этот параметр, выходные увеличения размера слова на 2 бита и когда вы очищаете этот параметр выходные увеличения размера слова на 11 битов.

Enable reset input port — Дополнительный сигнал сбросаoff (значение по умолчанию) | onВыберите этот параметр, чтобы включить порт reset.

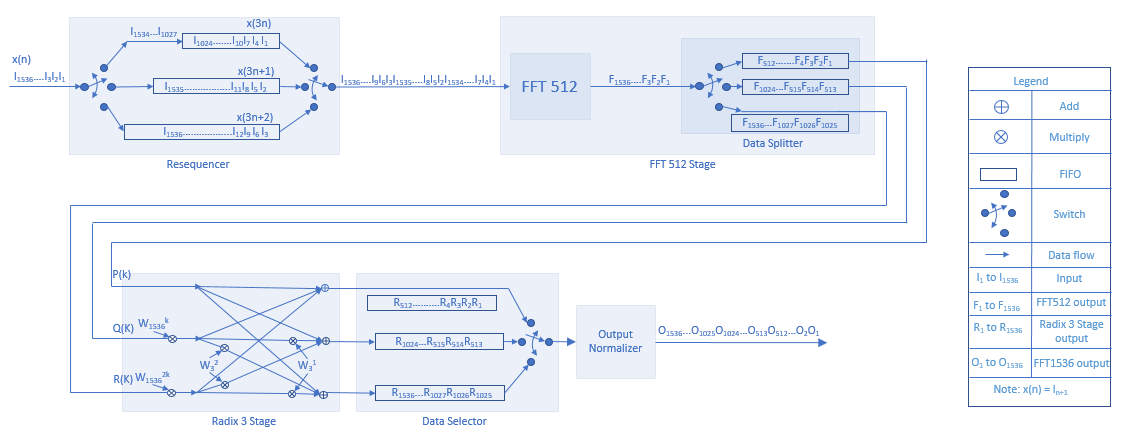

Чтобы спроектировать блок FFT 1536, основание, 3 алгоритма децимации вовремя (DIT) реализованы. Входная последовательность x (n) для всего n = {0,1,2.... 1535} разделен на три последовательности DIT, x (3n), x (3n+1), x (3n+2) для всего n = {0,1,2.... 511}.

Это уравнение задает БПФ 1 536 расчетов данной последовательности x (n).

Уравнение может быть реализовано путем деления его в три части, где P (k), Q (k), R (k) являются N/3 (БПФ 512) БПФ точки x (3n), x (3n+1) и x (3n+2), соответственно. Здесь, N = 1536, и k = 0,1,2....., 511.

Эта схема показывает внутреннюю архитектуру блока и как входные потоки последовательности через компоненты блока.

Входная последовательность x (n) демультиплексируется в три последовательности DIT, x (3n), x (3n+1), x (3n+2), каждая длина 512. Три памяти сначала введенного сначала выведенного (FIFO) хранит эти последовательности. Эти последовательности DIT сериализируются и передаются потоком через блок FFT 512.

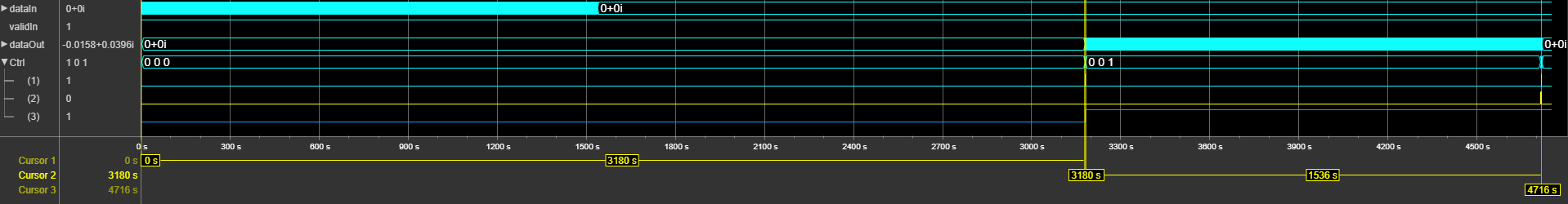

Это изображение показывает выходную форму волны блока, когда управляется с параметрами конфигурации по умолчанию. Блок обеспечивает выходные данные после задержки 3 180 тактов. Продолжительность выходных данных между start (Ctrl.(1)) и end (Ctrl.(2)), о котором сигнализирует элемент управления выводом, является 1 536 тактами.

Производительность синтезируемого HDL-кода меняется в зависимости от вашей цели и опций синтеза. Эта таблица показывает, что результаты синтеза данных ресурсов и данных о производительности блока с параметрами конфигурации по умолчанию, наряду с функцией нормализации включили, и с входные данные в fixdt(1,17,15) формат. Сгенерированный HDL предназначен к плате Xilinx® Zynq® XC7Z045-FFG900-2 FPGA. Проект достигает частоты часов 355 МГц.

| Ресурс | Используемый номер |

|---|---|

| LUTs | 7330 |

| Регистры | 9325 |

| Блокируйте RAM | 18 |

| DSPS | 36 |

Этот блок поддерживает генерацию кода C/C++ для акселератора Simulink® и быстрых режимов Accelerator и для генерации компонента DPI.

HDL Coder™ обеспечивает дополнительные параметры конфигурации, которые влияют на реализацию HDL и синтезируемую логику.

Этот блок имеет одну, архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. |

| InputPipeline | Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

| OutputPipeline | Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. |

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.