Можно экспортировать функцию MATLAB® как компонент с интерфейсом программирования на машинном языке (DPI) для использования в симуляции SystemVerilog. Перенесите сгенерированный код C с оберткой DPI, которая передает с SystemVerilog тонкую функцию интерфейса в симуляции SystemVerilog.

Для MATLAB вы генерируете компонент с помощью dpigen функция.

Примечание

У вас должна быть лицензия MATLAB Coder™, чтобы использовать эту функцию.

Поддерживаемые типы данных MATLAB преобразованы в типы данных SystemVerilog, как показано в этой таблице. При использовании dpigen функция, используйте PortsDataType свойство выбрать Compatible C type, Logic vector, или Bit vector типы данных.

Сгенерированные типы SystemVerilog

| MATLAB | SystemVerilog | ||

|---|---|---|---|

| Совместимый тип C | Логический вектор | Битовый вектор | |

uint8 | byte unsigned | logic [7:0] | bit [7:0] |

uint16 | shortint unsigned | logic [15:0] | bit [15:0] |

uint32 | int unsigned | logic [31:0] | bit [31:0] |

uint64 | longint unsigned | logic [63:0] | bit [63:0] |

int8 | byte | logic signed [7:0] | bit signed [7:0] |

int16 | shortint | logic signed [15:0] | bit signed [15:0] |

int32 | int | logic signed [31:0] | bit signed [31:0] |

int64 | longint | logic signed [63:0] | bit signed [63:0] |

logical | byte unsigned | logic [0:0] | bit [0:0] |

fi (тип данных с фиксированной точкой) | Зависит от размера слова фиксированной точки. Если размер слова фиксированной точки больше размера слова хоста (например, 64-битный по сравнению с 32-битным), то этот тип данных не может быть преобразован в тип данных SystemVerilog MATLAB Coder, и вы получите ошибку. Если размер слова фиксированной точки меньше чем или равен размеру слова хоста, MATLAB Coder преобразует тип данных с фиксированной точкой во встроенный тип C. |

Логическая длина вектора ( |

Длина битового вектора ( |

single | shortreal | ||

double | real | ||

complex | Кодер сглаживает комплексные сигналы в действительные и мнимые части в компоненте SystemVerilog. | ||

| векторы, матрицы | массивы Например, 4 2 матрица в MATLAB преобразована в одномерный массив восьми элементов в SystemVerilog. По умолчанию кодер сглаживает матрицы в порядке развертывания по столбцам. Чтобы превратиться в упорядоченный по строкам порядок, используйте | ||

structure | Кодер сглаживает элементы структуры в отдельные порты в компоненте SystemVerilog. | ||

| перечислимые типы данных | enum | ||

Функция dpigen автоматически компилирует разделяемую библиотеку, должен был запустить экспортируемый компонент DPI в среде SystemVerilog. Make-файл, который создает разделяемую библиотеку, имеет дополнительный _rtw.mk. Например, для fun.m, именем make-файла является fun_rtw.mk.

Во время компиляции, функционального dpigen генерирует файл библиотеки.

Windows® 64: function_win64.dll

Linux®: function.so

function имя функции MATLAB, от которой вы сгенерировали компонент DPI.

Примечание

Если вы используете 64-битный MATLAB на Windows, вы получаете 64-битный DLL, который может использоваться только с 64-битным симулятором HDL.

Убедитесь, что ваша версия MATLAB совпадает с вашей версией симулятора HDL.

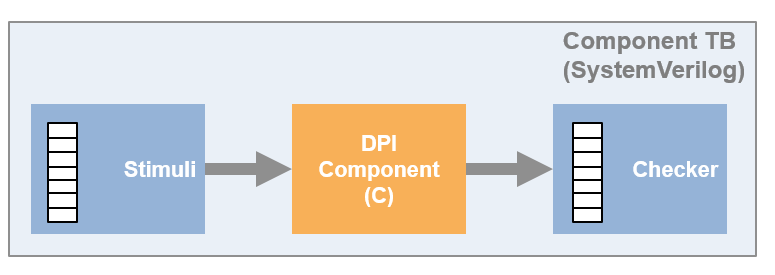

Функция dpigen также создает испытательный стенд. Можно использовать этот испытательный стенд, чтобы проверить, что сгенерированный компонент SystemVerilog функционально эквивалентен исходной функции MATLAB. Генератор запускает ваш код MATLAB, чтобы сохранить векторы входных и выходных данных для использования в испытательном стенде. Этот испытательный стенд не предназначается как замена для места размещения тестирования системы для вашего собственного приложения. Однако можно использовать сгенерированный испытательный стенд в качестве стартового примера при создании собственного места размещения тестирования системы.

C и заголовочные файлы из вашего алгоритма, сгенерированного MATLAB Coder

C и заголовочные файлы для обертки DPI, сгенерированной HDL Verifier™

Файл SystemVerilog, который отсоединяет компонент и добавляет управляющие сигналы

Файл пакета SystemVerilog, который содержит все объявления функции компонента DPI

Испытательный стенд SystemVerilog (с -testbench опция)

Файлы данных используются с симулятором HDL (с -testbench опция)

Скрипты симулятора HDL, такие как *.do или *.sh (с -testbench опция)

Make-файл *.mk

Весь код SystemVerilog сгенерирован функцией dpigen содержит набор управляющих сигналов и Initialize функция.

clk: часы синхронизации

clk_enable: часы включают

reset: асинхронный сброс

Initialize функция вызвана в начале симуляции.

Например:

import "DPI" function void DPI_Subsystem_initialize();

Если асинхронный сигнал сброса высок (идет от 0 до 1), Initialize называется снова.

При симуляции компонента DPI в среде HDL, resetчасы, и clk_enable ведите себя можно следующим образом:

Когда clk_enable 0, выходная функция DPI не выполняется, и выходные значения не обновляются.

Когда clk_enable 1 и reset 0, выходная функция DPI выполняется на положительном ребре сигнала часов.

Когда reset 1, внутреннее состояние компонента DPI установлено в свое начальное значение. Это действие эквивалентно использованию clear функция в MATLAB, чтобы обновить персистентные переменные. Затем выходные значения затем отражают начальное состояние компонента DPI и текущие входные значения. Для получения дополнительной информации о персистентных переменных смотрите Персистентные Переменные.

Аргументы переменного размера не поддерживаются.

Большие числа фиксированной точки, которые превышают системный размер слова, не поддерживаются.

Некоторая оптимизация, такая как сворачивание констант, не поддерживается, потому что они изменяют интерфейс сгенерированной функции C. Для получения дополнительной информации смотрите Оптимизацию MATLAB Coder в Сгенерированном коде (MATLAB Coder).

HDL Verifier ограничивает матрицы и векторы к одномерным массивам в SystemVerilog. Например, 4 2 матрица в MATLAB преобразована в одномерный массив восьми элементов в SystemVerilog.

Коллбэк PostCodegen в объектах конфигурации не поддерживается.