Чтобы отредактировать XML-файл определения платы, сначала сделайте его writeable. Если файл только для чтения, Редактор Совета FPGA только позволяет вам просмотреть информацию о конфигурации платы. Вы не можете изменить ту информацию.

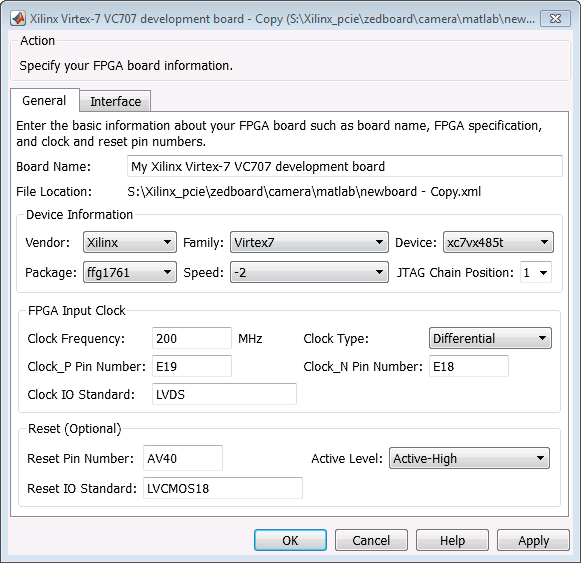

Board Name: Уникальное имя платы

Device Information:

Vendor: Xilinx или Altera

Family: Семейство зависит от заданного поставщика. Смотрите файл спецификации платы для применимых настроек.

Device: Устройство зависит от заданного поставщика и семейства. Смотрите файл спецификации платы для применимых настроек.

Для плат Xilinx® только:

Package: Пакет зависит от заданного поставщика, семейства и устройства. Смотрите файл спецификации платы для применимых настроек.

Speed: Скорость зависит от пакета. Смотрите файл спецификации платы для применимых настроек.

JTAG Chain Position: Значение указывает на стартовую позицию для цепи JTAG. Консультируйтесь с файлом спецификации платы для этой информации.

FPGA Input Clock. Детали часов требуются и для FIL и для рабочих процессов Под ключ. Можно найти всю необходимую информацию в файле спецификации платы.

Clock Frequency. Должен быть от 5 до 300. Для интерфейса Ethernet предложенные тактовые частоты равняются 50, 100, 125, и 200 МГц.

Clock Type: Single_Ended или Differential.

Clock Pin Number (Single_Ended) — Должен быть задан. Пример: N10.

Clock_P Pin Number (Дифференциал) — Должен быть задан. Пример: E19.

Clock_N Pin Number (Дифференциал) — Должен быть задан. Пример: E18.

Clock IO Standard — Программируемый Стандарт ввода-вывода, чтобы использовать, чтобы сконфигурировать вход, выведите, или двунаправленные порты. Например, LVDS.

Reset (Optional). Если вы хотите указать на сброс, найдите ПИН-код и активный уровень в файле спецификации платы, и введите ту информацию.

Reset Pin Number. Отпуск, пустой, если у вас нет того.

Active Level : Active-Low или Active-High.

Reset IO Standard — Программируемый Стандарт ввода-вывода, чтобы использовать, чтобы сконфигурировать вход, выведите, или двунаправленные порты. Например, LVCMOS33.

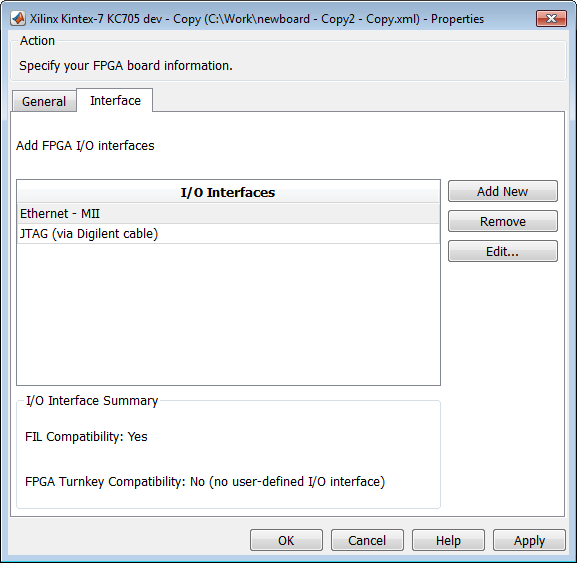

Страница Interface описывает поддерживаемые Интерфейсы ввода-вывода FPGA. Выберите любой перечисленный интерфейс и нажмите View, чтобы видеть Signal List. Если файл определения платы имеет разрешение записи, вы можете также интерфейс Add New, Edit интерфейс или Remove интерфейс.

Примечание

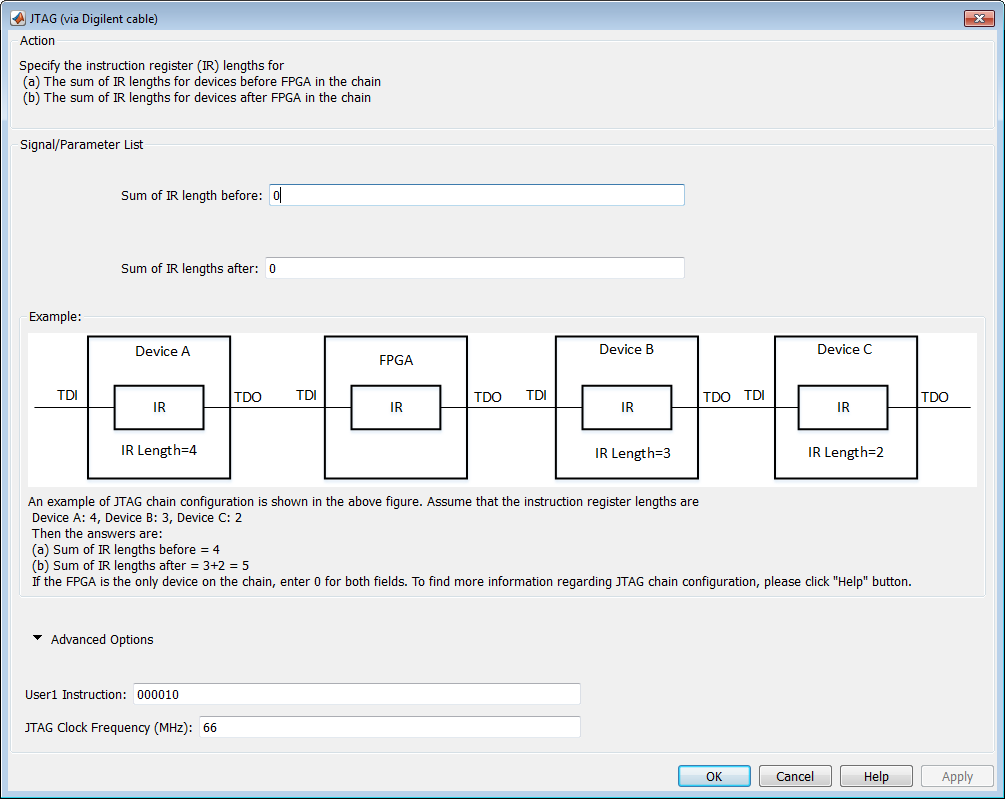

Введите информацию для настройки кабеля JTAG тщательно. Если настройки являются неправильными, ошибки симуляции, и не работает. Если вы все еще не уверены в том, как установить ваш кабель JTAG после чтения этих инструкций, свяжитесь с технической поддержкой MathWorks® с подробной информацией о вашей плате.

Signal/Parameter List — Предоставьте сумму длин регистров команд (IR) для всех устройств до и после FPGA в цепи.

Если FPGA является единственным элементом в цепи устройства, используйте нули и в Sum of IR length before и в Sum of IR length after.

Если вы используете устройство Zynq®, и это - единственный элемент в цепи устройства, введите 4 в Sum of IR length before и 0 в Sum of IR length after.

Если ваша плата не удовлетворяет ни одному из тех условий, следуйте этим инструкциям, чтобы получить длины IR:

Соедините плату FPGA со своим использующим компьютеры кабель JTAG. Включите плату.

Убедитесь, что вы установили драйверы кабеля во время установки Vivado®.

Откройте менеджера по Оборудованию Vivado и выберите Open a new hardware target. В диалоговом окне сводные данные длин IR для всех устройств для той цели.

Суммируйте длины IR перед FPGA и введите общее количество в Sum of IR length before. Суммируйте длины IR после FPGA и введите общее количество в Sum of IR length after.

Менеджер по Оборудованию Vivado не может распознать длину IR менее общих устройств. Для этих устройств консультируйтесь с руководством устройства для длины регистра команд.

Advanced Options — Если значения по умолчанию различные как наиболее распространенные настройки для многих устройств, установите параметры JTAG Clock Frequency (MHz) и User1 Instruction. Наиболее распространенными настройками является 000010 и 66, соответственно.

User1 Instruction — Инструкция JTAG USER1, заданная в примитивном Xilinx Bscane2. Этот бинарный номер инструкции, заданный Xilinx, варьируется с устройства на устройство. Для большинства устройств с 7 рядами этой инструкцией является 000010. Если ваше устройство имеет различное значение, введите его в этот параметр.

Чтобы найти это значение, посмотрите на bsd файл для вашего определенного устройства, найденного в вашей установке Vivado. Например, для устройства XA7A32T-CPG236, bsd файл расположен в Vivado\2014.2\data\parts\xilinx\artix7\aartix7\xa7a35t\cpg236.

Откройте этот файл. USER1 значением является 000010. Введите это значение в User1 Instruction.

"USER1 (000010),"

JTAG Clock Frequency (MHz) — Тактовая частота используется схемой JTAG. Это значение варьируется устройством. Можно найти это значение в том же bsd файл описан под User1 Instruction. Например, тактовая частота JTAG составляет 66 МГц для устройства XA7A32T-CPG236:

attribute TAP_SCAN_CLOCK of TCK : signal is (66.0e6, BOTH);