Проверки блока assertion DPI, является ли его входной сигнал нулем. Используйте этот блок, чтобы проверять, что ваш испытательный стенд Simulink® ведет себя как ожидалось путем создания Булевого выражения и соединения его с блоком. Генерация SystemVerilog создает мгновенное утверждение в вашем сгенерированном модуле. Используйте этот блок, чтобы проверять, что ваш стимул ведет себя как ожидалось и в вашем Simulink и в средах SystemVerilog.

В этом примере показано, как создать модель с блоком утверждения, который испускает предупреждение, когда выход блока усиления является нулем. Затем используйте в противоречии с, отображают вывод модели.

Создайте модель Simulink

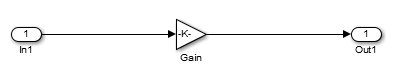

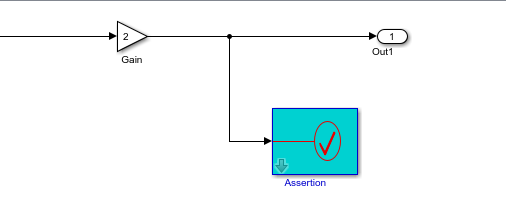

Модель в качестве примера имеет один блок усиления. Этот пример создает предупреждение каждый раз усиление, выход является нулем.

Откройте Simulink Block Library> Commonly Used Blocks.

Добавьте блок Inport.

Дважды кликните этот блок, чтобы открыть его параметры. Установите значение Gain к 2.

Добавьте блок Outport.

Соедините все блоки как показано в предыдущей схеме.

Добавьте и сконфигурируйте блок утверждения

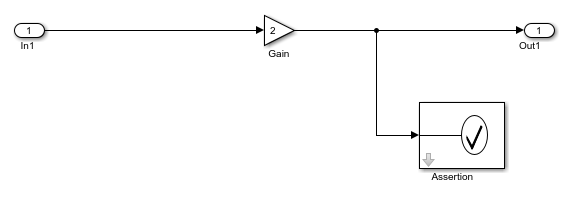

Найдите блок Assertion в структурном виде Libraries путем выбора HDL Verifier> For Use with DPI-C SystemVerilog. Добавьте этот блок в свою модель, затем соедините выход блока Gain к входу блока утверждения.

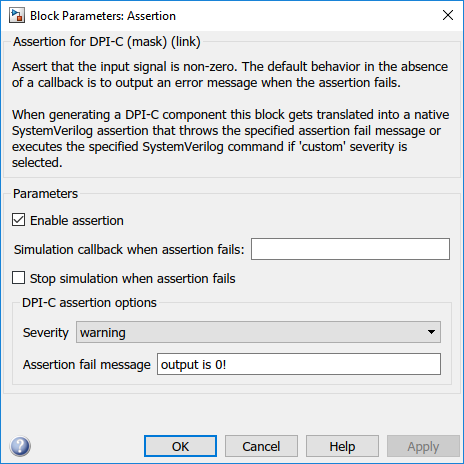

Этот пример использует блок Assertion, чтобы контролировать Gain выход и возвратить предупреждение, когда сигнал является нулем. Дважды кликните блок Assertion, чтобы сконфигурировать его параметры. Установите Severity на warning и Assertion fail message к "output is 0!". Убедитесь, что Enable assertion выбран.

Примечание

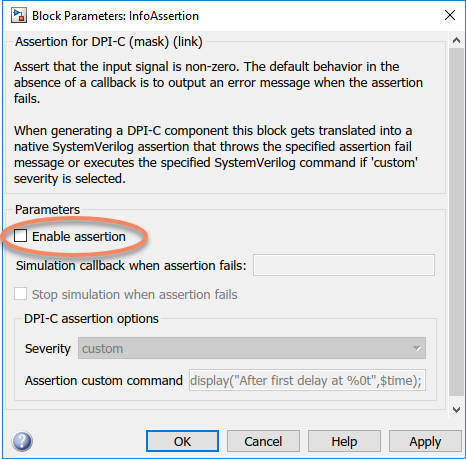

Раздел Parameters управляет выполнением Simulink, и они идентичны параметрам в блоке Simulink Assertion (Simulink). Управление DPI-C assertion options поведение утверждения только в сгенерированном SystemVerilog.

Настройте утверждение

Настройте утверждение установкой Severity к custom и ввод пользовательской команды SystemVerilog в поле Assertion custom command. Эта команда может включать системные задачи, такие как $display или $time.

Можно далее настроить поведение утверждения с помощью сгенерированного DPI_getAssertionInfo(obj) Функция SystemVerilog. Эта функция проверяет на выполняемые утверждения и возвращает всю информацию, зарегистрированную для того утверждения в массиве структур SystemVerilog. Для каждого утверждения, которое выполнялось за тот такт, функция возвращает Statusсообщение, и Severity из утверждения.

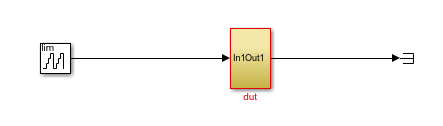

Запустите симуляцию в Simulink

Перед симуляцией, подключение источник стимула и приемник к вашей подсистеме. Этот пример использует счетчик, который генерирует 0-1-2-3 последовательности.

Чтобы создать и запустить симуляцию, нажмите кнопку Run на панели инструментов.

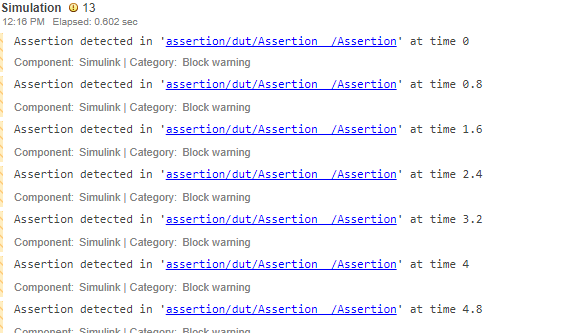

Отметьте предупреждения в блоке утверждения в выходе.

Сгенерируйте компонент SystemVerilog DPI

На Simulink Apps вкладка нажимают HDL Verifier. Затем на вкладке HDL Verifier нажмите C Code Settings. Диалоговое окно Configuration Parameters открывается на Code Generation.

В System target file нажмите Browse и выберите systemverilog_dpi_grt.tlc.

Если у вас есть лицензия на Embedded Coder®, можно выбрать целевой systemverilog_dpi_ert.tlc. Эта цель позволяет вам получать доступ к своим опциям генерации дополнительного кода (на панели Генерации кода в Параметрах конфигурации Модели).

В группе Генерации кода нажмите SystemVerilog DPI.

Чтобы включить автоматическую генерацию испытательного стенда, установите флажок Generate test bench.

Нажмите OK, чтобы принять эти настройки и закрыть диалоговое окно Configuration Parameters.

На вкладке HDL Verifier нажмите Generate DPI Component.

В коде Сборки для диалогового окна подсистемы нажмите Build.

Компонент SystemVerilog сгенерирован как dut_build/dut_dpi.sv в вашей текущей рабочей папке. Кроме того, файл пакета включая объявления функции сгенерирован в как dut_build/dut_dpi_pkg.sv в вашей текущей рабочей папке.

Запустите симуляцию SystemVerilog

В HDL Verifier вкладка нажимают Select Simulator, чтобы открыть Параметры конфигурации на SystemVerilog DPI pane. Затем выберите средство моделирования из списка HDL simulator. Нажмите OK.

Чтобы запустить средство моделирования в режиме GUI, расширьте кнопку Run Testbench и выберите Launch Simulator in GUI Mode.

Для ModelSim®or Questa® введите следующую команду, чтобы запустить вашу симуляцию.

do run_tb_mq.do

Заметьте предупреждения симуляции, выведенные утверждением:

run -all # ** Warning: assertion:14:output is 0! # Time: 40 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 80 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 120 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 160 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 200 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 240 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 280 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 320 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 360 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 400 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 440 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 480 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 520 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # **************TEST COMPLETED (PASSED)************** # ** Note: $finish : ./dut_dpi_tb.sv(62) # Time: 542 ns Iteration: 0 Instance: /dut_dpi_tb # End time: 14:16:43 on Dec 29,2017, Elapsed time: 0:00:04 # Errors: 0, Warnings: 13

После выполнения симуляции SystemVerilog со сгенерированным утверждением ваш файл журнала выводит предупреждения и ошибки. Чтобы идентифицировать, какой блок утверждения породил определенное предупреждение или вывод ошибок, используйте hilite_system (Simulink) функция.

Каждое предупреждение отображает номер, идентифицирующий определенный блок Assertion, который сгенерировал то предупреждение. Тот номер является идентификатором Simulink (SID) того блока. Например, следующее показывает предупреждение, сгенерированное блоком утверждения с SID номер 14.

# ** Warning: assertion:14:output is 0!

Чтобы подсветить блок, который сгенерировал это предупреждение, выполните следующий код в своем командном окне MATLAB®.

hilite_system('assertion:14')

Для получения дополнительной информации об Идентификаторах Simulink смотрите Идентификаторы Simulink (Simulink).

Можно отключить любой блок утверждения из выполнения или в окружении Simulink или в среде SystemVerilog. Отключите утверждение в Simulink, если вы хотите утверждение, проигнорированное и в Simulink и в SystemVerilog. Отключите утверждение в SystemVerilog, если вы не хотите регенерировать код от Simulink, но хотеть способность отключить утверждения во время симуляции SystemVerilog.

Отключение Утверждений в Simulink. Можно отключить блок DPI-C Assertion из проверки его входного сигнала или испускания предупреждений или ошибок путем снятия флажка Enable assertion в параметрах блоков Assertion.

Снятие этого флажка отключает утверждение от испускания любых предупреждений или ошибок и генерации утверждения SystemVerilog.

Отключение Утверждений в SystemVerilog. В среде SystemVerilog можно отключить утверждение путем обеспечения Идентификатора Simulink как параметра командной строки к симулятору HDL. Например, при использовании ModelSim и принятия SID 14, можно отключить выход любых предупреждений, сообщений об ошибке или пользовательских команд, произведенных блоком Assertion со следующим плюс аргумент:

vsim -c -voptargs=+acc -sv_lib ../dut_win64 work.dut_dpi_tb +assertion:14