HDL Verifier™ обеспечивает два типа испытательных стендов, которые генерируют компонент языка C и интегрируют его в испытательный стенд SystemVerilog с интерфейсом программирования на машинном языке (DPI). Один испытательный стенд проверяет сгенерированный компонент C по сохраненным векторам данных от вашей подсистемы Simulink®. Другой испытательный стенд проверяет сгенерированный HDL-код по компоненту C, сгенерированному из целой модели Simulink.

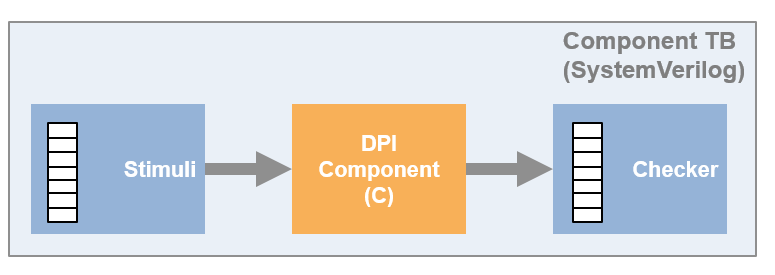

Испытательный стенд компонента — Когда вы генерируете компонент C от Подсистемы Simulink для использования в качестве компонента DPI, можно опционально сгенерировать испытательный стенд SystemVerilog. Испытательный стенд проверяет сгенерированный компонент DPI по векторам данных из вашей модели Simulink. Эта функция доступна в диалоговом окне Model Configuration Parameters под Code Generation. Смотрите Генерируют Компонент SystemVerilog DPI.

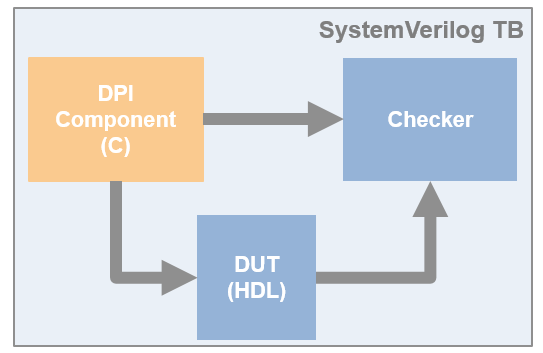

Испытательный стенд HDL-кода — Когда вы генерируете HDL-код от подсистемы, с помощью HDL Coder™, можно опционально сгенерировать испытательный стенд SystemVerilog. Этот испытательный стенд сравнивает выход реализации HDL против результатов модели Simulink. Можно получить доступ к этой функции в HDL Workflow Advisor под HDL Code Generation> Set Testbench Options, или в диалоговом окне Model Configuration Parameters, под HDL Code Generation> Test Bench. В качестве альтернативы для доступа из коммандной строки, набор GenerateSVDPITestBench свойство makehdltb (HDL Coder). Смотрите проверяют проект HDL Используя испытательный стенд (HDL Coder) SystemVerilog DPI.

Оба типа испытательных стендов требуют лицензии Simulink Coder™.

Ограничения

HDL Verifier преобразует матрицы и векторы к одномерным массивам в SystemVerilog. Например, 4 2 матрица в Simulink преобразована в одномерный массив восьми элементов в SystemVerilog.

Эти подсистемы не поддерживают генерацию испытательного стенда DPI:

Триггируемая подсистема

Enabled подсистема

Подсистема с портом действия

Генератор компонента SystemVerilog DPI также создает испытательный стенд. Можно использовать этот испытательный стенд, чтобы проверить, что сгенерированный компонент SystemVerilog функционально эквивалентен исходной Подсистеме Simulink. Испытательный стенд избавляет векторы данных от вашей симуляции Simulink, чтобы применяться как стимулы и проверять по выходу компонента. Этот испытательный стенд не предназначается как замена для места размещения тестирования системы для вашего собственного приложения. Однако можно использовать сгенерированный испытательный стенд в качестве стартового примера для собственного места размещения тестирования системы.

Если вы позволяете войти в систему тестовые точки в своей модели, сгенерированный испытательный стенд также сравнивает их значения сигналов в компоненте SystemVerilog с регистрируемыми значениями от Simulink.

Примечание

HDL Verifier не поддерживает генерацию испытательного стенда для пользовательского сгенерированного кода SystemVerilog. Смотрите Индивидуальную настройку.

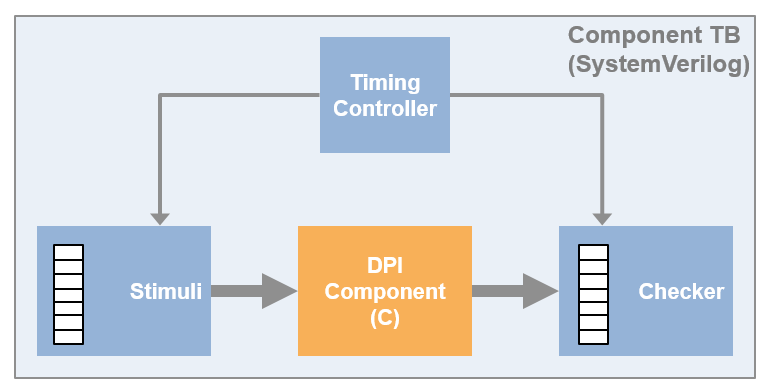

Когда ваша подсистема содержит сигналы больше чем с одной частотой дискретизации, сгенерированный испытательный стенд включает контроллер синхронизации модуль. Контроллер синхронизации генерирует входные сигналы часов на соответствующих уровнях. Введите стимулы, и ожидаемые выводы данных применяются и проверяются согласно их частотам дискретизации.

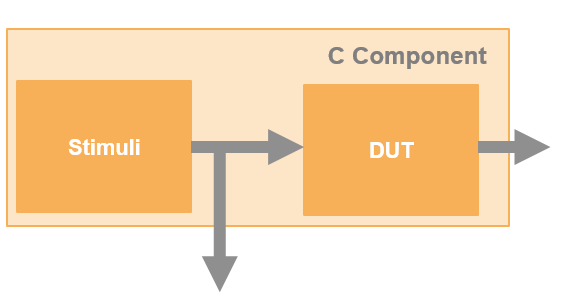

Когда вы генерируете HDL-код от подсистемы, с помощью HDL Coder, можно также сгенерировать испытательный стенд SystemVerilog DPI. Этот испытательный стенд сравнивает выход реализации HDL против результатов модели Simulink. В дополнение к коду С для вашей подсистемы DUT кодер также генерирует код С для фрагмента вашей модели, которая генерирует входные стимулы. Генерация этого испытательного стенда быстрее, чем испытательный стенд HDL по умолчанию для больших наборов данных. Это преимущество состоит в том, потому что кодер не запускает модель Simulink, чтобы получить векторы входных и выходных данных. Сгенерированный компонент C вычисляет входные стимулы и выходные результаты для сравнения с реализацией HDL.

Сгенерированный испытательный стенд SystemVerilog включает:

Сгенерированный Verilog® или код VHDL® для вашей подсистемы

Сгенерированный компонент C

Код, чтобы сравнить выход HDL-кода с выходом компонента C.

Запустите этот испытательный стенд, чтобы проверить, что сгенерированный HDL-код реализует тот же алгоритм как ваша модель Simulink.