В этом примере показано, как выполнить верификацию модели временного интервала с помощью блоков Simulink® Design Optimization™ Model Verification. Во время верификации временного интервала программное обеспечение контролирует сигнал проверять, соответствует ли это характеристикам временного интервала, таким как характеристики переходного процесса и верхние и более низкие амплитуды, или отслеживает опорный сигнал.

Можно также использовать блоки из библиотек Simulink и Simulink Control Design™ Model Verification, чтобы спроектировать комплексную логику утверждения для временного интервала и верификации частотного диапазона и контроля сигналов. Можно создать тесты симуляции для модели с помощью менеджера по Верификации в Signal Builder.

Открытая модель Simulink.

sys = 'sldo_model1_stepblk';

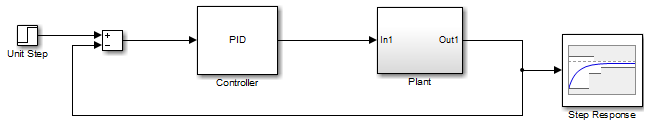

open_system(sys);

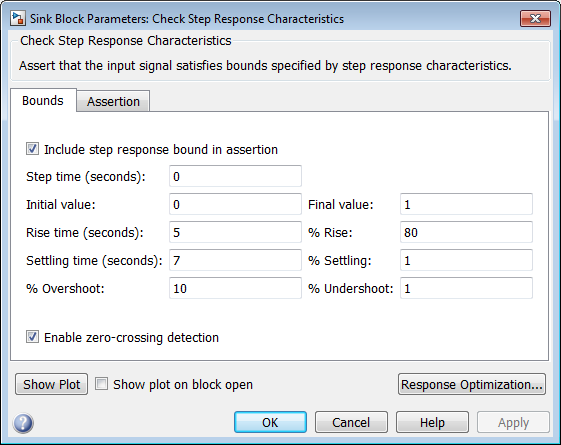

Модель включает блок Step Response, который является блоком Check Step Response Characteristics из библиотеки Simulink Design Optimization Model Verification и имеет границы переходного процесса по умолчанию.

В Редакторе Simulink, под Simulation, нажимают Run.

Блок утверждает многократно в процессе моделирования, потому что сигнал, с которым соединяется блок, нарушает заданные границы. Предупреждения утверждения появляются в командном окне MATLAB®.

Можно оптимизировать параметры модели, чтобы удовлетворить границам и устранить предупреждения утверждения. Смотрите Оптимизацию Проекта, чтобы Удовлетворить Требования Переходного процесса (графический интерфейс пользователя).