Выровняйте два потока пиксельных данных

Vision HDL Toolbox / Утилиты

Блок Pixel Stream Aligner синхронизирует потоки на два пикселя путем задержки одного потока, чтобы совпадать с синхронизацией ссылочного потока. Много алгоритмов Vision HDL Toolbox™ задерживают пиксельный поток, и сумма задержки может измениться, когда вы настраиваете параметры алгоритма. Можно использовать этот блок, чтобы выровнять потоки для того, чтобы наложить, сравнить или объединить два потока такой как в Гауссовой операции размытости. Соедините задержанный поток с refPixel и входными портами refCtrl, и более ранний поток к входным портам ctrl и pixel.

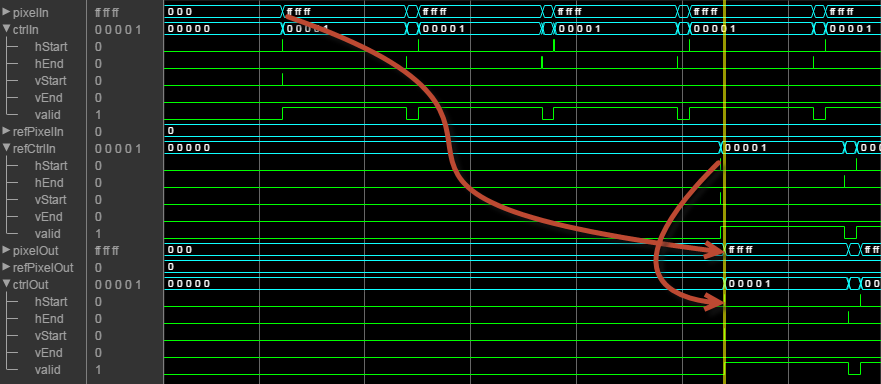

Эта схема формы волны показывает входные потоки, pixelIn и refPixelIn, и их связанные управляющие сигналы. Ссылочный входной кадр запускается позже, чем pixelIn система координат. Выходные сигналы показывают, что блок задерживает pixelIn совпадать со ссылочным потоком, и что оба потока вывода совместно используют управляющие сигналы. Форма волны показывает короткую задержку между входом refCtrl и выход refCtrl. В этой симуляции, чтобы вместить задержку четырех линий между входными потоками, параметр Maximum number of lines должен быть установлен на по крайней мере 4.

Этот блок использует пиксельный интерфейс потоковой передачи с pixelcontrol соедините шиной для сигналов управления кадром. Этот интерфейс позволяет блоку действовать независимо от размера изображения и формата. Все блоки Vision HDL Toolbox используют тот же интерфейс потоковой передачи. Блок принимает и возвращает скалярное пиксельное значение и шину, которая содержит пять управляющих сигналов. Управляющие сигналы указывают на валидность каждого пикселя и его местоположения в системе координат. Чтобы преобразовать систему координат (пиксельная матрица) в последовательный пиксельный поток и управляющие сигналы, используйте блок Frame To Pixels. Для полного описания интерфейса смотрите Пиксельный Интерфейс Потоковой передачи.

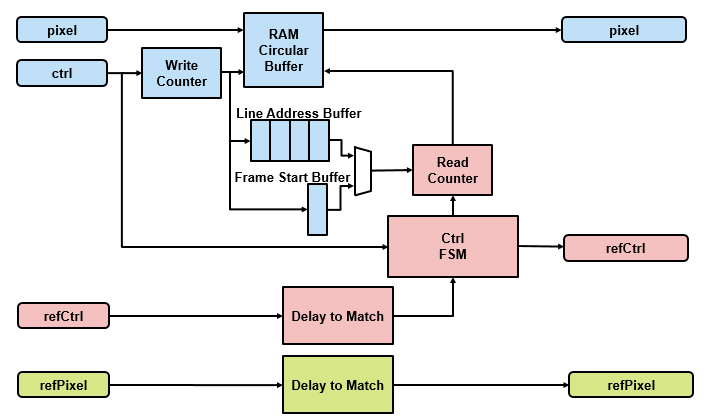

Блок хранит данные от входного порта pixel до кольцевого буфера и затем читает строки, чтобы выровняться со ссылочными управляющими сигналами. Блок также хранит адрес запуска каждой линии. Чтобы совпадать с добавленной задержкой обработки буферного информационного канала, блок задерживает ссылочные пиксельные данные и управляющие сигналы приблизительно для 10 циклов.

Схема показывает архитектуру блока. Кольцевой буфер RAM является памятью о 2M пиксели, где M является Maximum number of lines + log2 (Line buffer size). Буфер адресов Линии имеет местоположения Maximum number of lines. Если количество ctrl.Hstart утверждения перед первым refCtrl.Hstart утверждение больше размера Буфера адресов Линии, блок перезаписывает и буферы и повреждает выход. В этой схеме Maximum number of lines равняется четырем, таким образом, четыре места существуют, чтобы сохранить адрес линии в буфере. Система координат Запускается, Буфер является одним местоположением, чтобы сохранить ctrl.Vstart. Задержка между этими двумя потоками должна быть меньше, время между системой координат запускается.

Когда вход pixel является вектором, блок реплицирует Кольцевой буфер RAM для каждого элемента вектора.