Вы генерируете HTML пользовательский отчет ядра IP по умолчанию, когда вы генерируете пользовательское ядро IP. Отчет описывает поведение и содержимое сгенерированного пользовательского ядра IP.

Раздел Summary показывает ваши настройки кодера, когда вы сгенерировали пользовательское ядро IP.

Следующая фигура является примером раздела Summary.

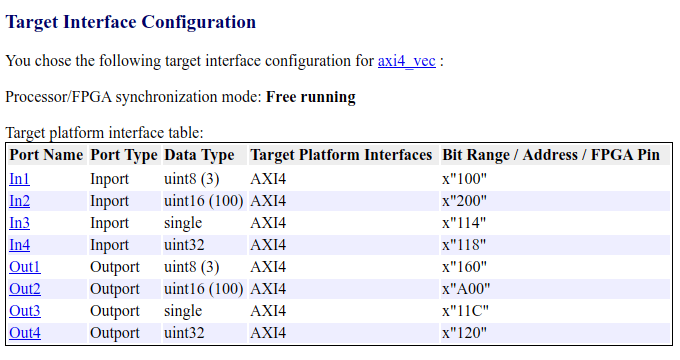

Раздел Target Interface Configuration показывает, как ваши порты DUT сопоставляют с интерфейсом целевого компьютера и режимом синхронизации процессора/FPGA.

Следующая фигура является примером раздела Target Interface Configuration.

Чтобы узнать больше о режимах синхронизации процессора/FPGA, смотрите Синхронизация FPGA и Процессор.

Чтобы узнать больше об интерфейсах целевой платформы, смотрите Пользовательскую Генерацию Ядра IP.

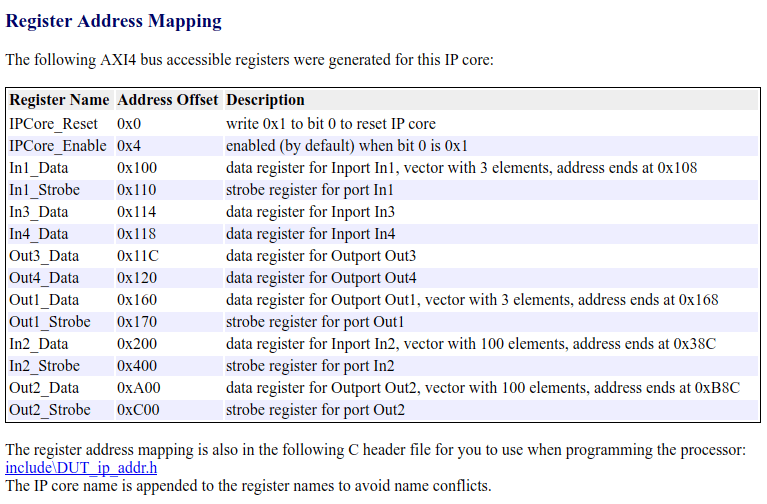

Раздел Register Address Mapping показывает смещения адреса для AXI4-облегченной шины доступные регистры в вашем пользовательском ядре IP и имя заголовочного файла C, который содержит те же смещения адреса.

Следующая фигура является примером раздела Register Address Mapping.

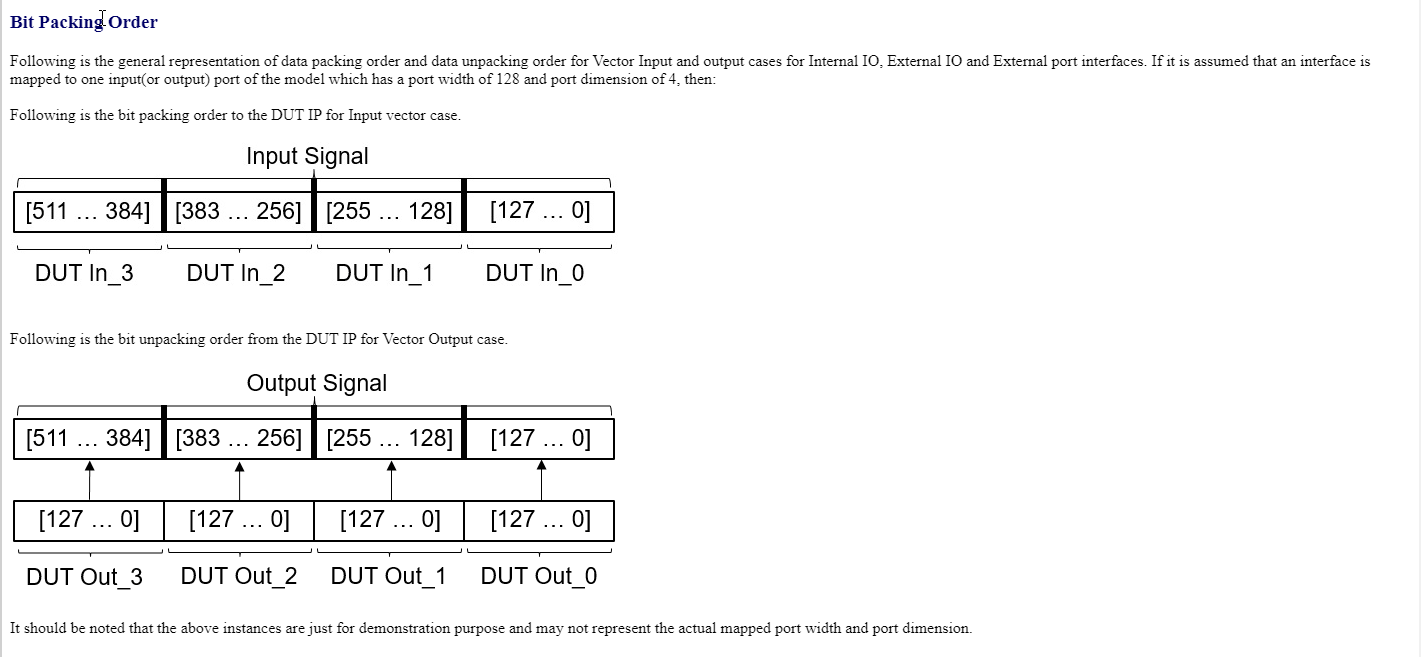

Раздел Bit Packing Order дает общий обзор порядка упаковки данных для векторных вводов и выводов для Внутреннего IO, Внешнего IO и интерфейсов Внешнего порта. Этот раздел только появляется, когда порт width для Внутреннего IO, Внешнего IO и Внешних портов установлен в больший, чем 128 битов шириной.

Это изображение является примером Бита, упаковывающего раздел Order:

Раздел IP Core User Guide дает общий обзор архитектуры системы, описывает процессор и режим синхронизации FPGA, и дает инструкции для интеграции ядра IP в вашей среде интегрирования встраиваемой системы.

Следующая фигура является примером описания архитектуры системы Руководства пользователя Ядра IP.

Следующая фигура является примером описания синхронизации процессора/FPGA.

Если вы используете векторные сигналы данных в интерфейсе DUT, отчет ядра IP отображает этот раздел, который показывает, как генератор кода синхронизирует векторные данные через интерфейс AXI4.

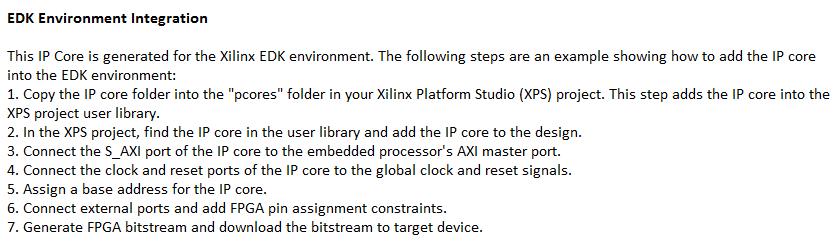

Следующая фигура является примером инструкций для интеграции ядра IP в вашу среду интегрирования встраиваемой системы на платформе Xilinx®. Если вы предназначаетесь для платформы Altera®, отчет отображает подобные инструкции для интеграции ядра IP в среду Altera Qsys.

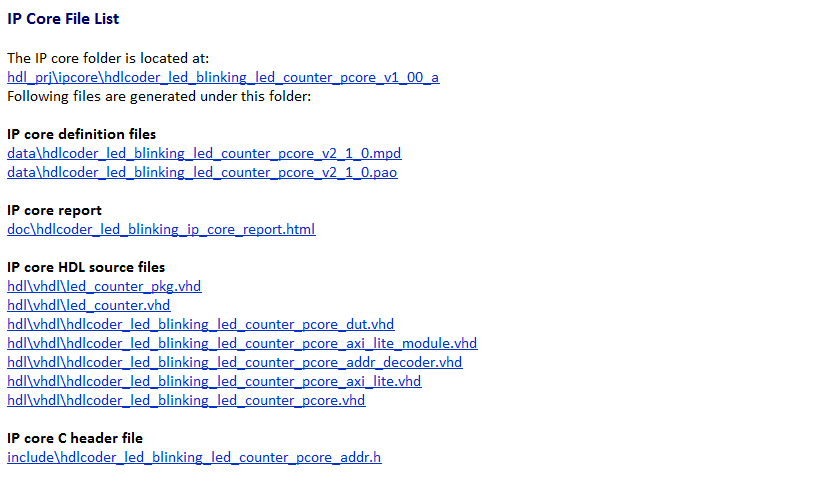

Раздел IP Core File List перечисляет файлы и папки, которые включают ваше пользовательское ядро IP.

Следующая фигура является примером списка файлов ядра IP.