Используйте HDL import, чтобы импортировать синтезируемый HDL-код в среду моделирования Simulink®. HDL import анализирует файл входа HDL и генерирует модель Simulink. Модель является средой блок-схемы, которая визуально представляет HDL-код в терминах функциональности и поведения. Путем импорта HDL-кода в Simulink можно проверить функциональность HDL-кода путем скомпилир и запущения симуляции на модели в основанной на модели среде симуляции. Можно также отладить внутренние сигналы путем логгирования сигналов как тестовых точек.

Генерации кода туда и обратно с импортом HDL не рекомендуют. Не используйте импорт HDL, чтобы импортировать HDL-код, который был ранее сгенерирован из модели Simulink при помощи программного обеспечения HDL Coder™. Модель Simulink, которую вы создаете, обычно на более высоком уровне абстракции. Модель, сгенерированная импортом HDL, может быть на более низком уровне абстракции. HDL-код вы генерируете от этой силы модели не быть применимыми для производственного кода.

Чтобы сгенерировать производственный HDL-код, разработайте свой алгоритм при помощи блоков Simulink, код MATLAB® или графики Stateflow®. Затем используйте HDL Coder, чтобы сгенерировать код.

Чтобы сгенерировать модель Simulink, убедитесь, что файл HDL вы импортируете:

Свободно от синтаксических ошибок.

Является синтезируемым.

Использование поддержало построения Verilog® для импорта.

Импортировать HDL-код, в командном окне MATLAB, запуск importhdl функция. Например, чтобы импортировать файл Verilog example.v, в командной строке, введите:

importhdl('example.v')Построения, которые вы используете в HDL-коде, могут вывести простые блоки Simulink, такие как Add и Product с блоками RAM, такими как Dual Rate Dual Port RAM. Для примеров, которые иллюстрируют различные модели Simulink, которые выведены, смотрите importhdl.

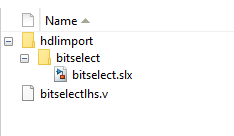

Сгенерированную модель Simulink называют в честь главного модуля в файле входа HDL, который вы задаете. Модель сохранена в hdlimport/TopModule путь относительно текущей рабочей папки. Например, если вы вводите файл с именем bitselectlhs.v к importhdl функция, которая имеет bitselect как главное имя модуля, сгенерированная модель Simulink имеет имя bitselect.slx, и сохранено в hdlimport/bitselect путь относительно текущей папки.

Когда вы запускаетесь importhdl функция, импорт HDL проверяет синтаксис и семантику входного HDL-кода. Семантическая верификация проверяет на построения инстанцирования модуля, неиспользуемые порты в определении модуля, списке чувствительности always блокируйтесь и так далее. Если импорт HDL перестал работать, importhdl предоставляет сообщение об ошибке и ссылку на имя файла и номер строки.

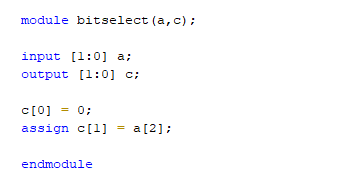

Например, рассмотрите этот код Verilog для bitselect модуль:

Когда вы запускаетесь importhdl функция, импорт HDL генерирует сообщение об ошибке:

Parser Error: bitselectlhs.v:6:2: error: Syntax Error near '['..

Сообщение об ошибке указывает, что существует синтаксическая ошибка в линии 6. Чтобы зафиксировать эту ошибку, измените синтаксис в оператор присваивания.

assign c[0] = 0;

Импорт HDL не поддерживает:

Импорт файлов VHDL.

Импорт файлов Verilog от папки только для чтения.

Генерация файлов предварительной обработки в файловой системе только для чтения, которые анализируют HDL-код, который вы вводите к importhdl функция.

Припишите экземпляры и комментарии, которые проигнорированы.

(#) задерживают значения, такие как #25, которые проигнорированы.

Типы данных перечисления.

Больше чем один сигнал часов.

Модули, которые являются многоскоростными.

Рекурсивное инстанцирование модуля.

Вывод Multiport Switch с больше, чем 1024 входные параметры. Если вы задаете больше, чем 1024 входные параметры с блоком Multiport Switch, который выведен из кода Verilog, импорт Verilog, генерируют ошибку. Ошибка сгенерирована, потому что среда моделирования Simulink не поддерживает больше, чем 1024 входные параметры для блока.

Обнаружение ROM из кода Verilog.

Импорт файлов HDL, которые используют неподдерживаемые построения Verilog. Смотрите Поддерживаемые Построения Verilog для Импорта HDL.

Импорт файлов HDL, которые используют неподдерживаемые шаблоны моделирования потока данных. Смотрите Неподдерживаемые Шаблоны Потока данных Verilog.