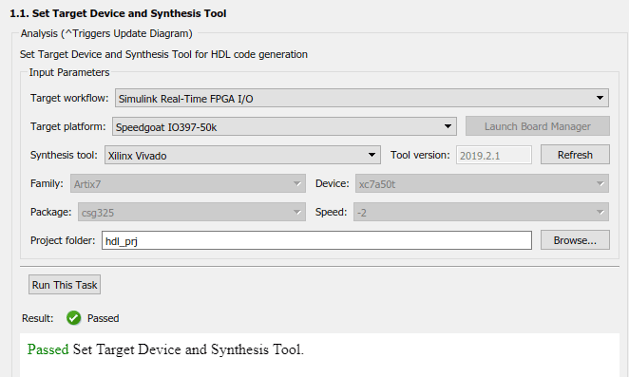

HDL Coder™ использует IP Core Generation инфраструктура рабочего процесса, чтобы сгенерировать допускающее повторное использование ядро IP HDL для Программируемых Simulink модулей ввода-вывода Speedgoat та поддержка Xilinx® Vivado®. Рабочий процесс представляет отчет ядра IP, который отображает целевую интерфейсную настройку и настройки генератора кода, которые вы задаете. Можно интегрировать ядро IP в больший проект путем добавления его в среде интегрирования встраиваемой системы. Смотрите Пользовательскую Генерацию Ядра IP.

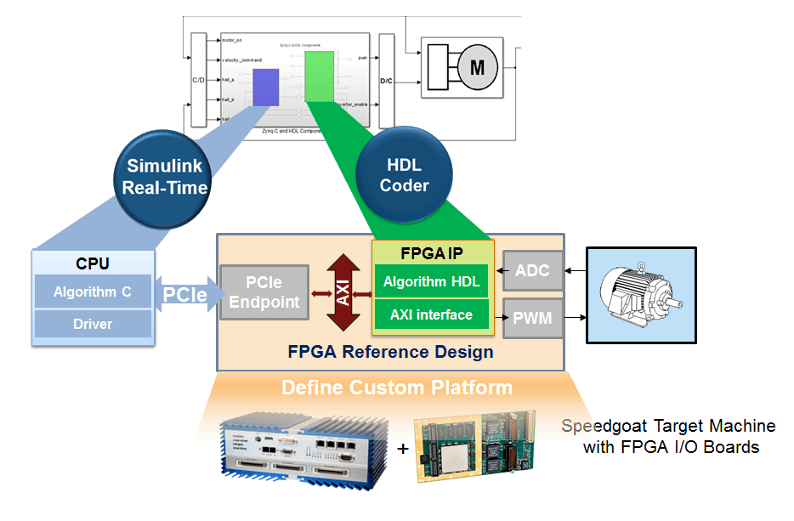

Этот рисунок показывает, как программное обеспечение генерирует ядро IP с интерфейсом AXI и интегрирует ядро IP в исходный проект FPGA.

Узнать о модулях ввода-вывода, что HDL Coder поддерживает с Simulink Real-Time FPGA I/O рабочий процесс, см. Поддержку FPGA Speedgoat с HDL Workflow Advisor.

Этот рабочий процесс имеет эти ключевые возможности:

Использование Xilinx Vivado как инструмент синтеза.

Генерирует допускающее повторное использование и ядро IP с обеспечением совместного доступа. Ядро IP группирует код RTL, заголовочный файл C и файлы определения ядра IP.

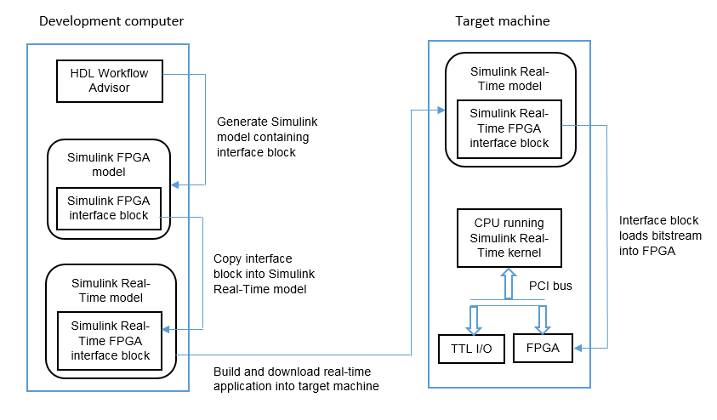

Создает проект для интеграции ядра IP в исходный проект Speedgoat.

Генерирует поток битов FPGA и загружает поток битов на целевой компьютер.

После создания потока битов FPGA рабочий процесс генерирует модель Simulink® Real-Time™. Модель является интерфейсной моделью подсистемы, которая содержит блоки, чтобы программировать FPGA и связаться с модулем ввода-вывода через шину PCIe во время выполнения в реальном времени.

IP Core Generation рабочий процесс не поддерживает:

Набор RAM Architecture к Generic RAM without clock enable.

Используя различные часы для ядра IP и интерфейса AXI. IPCore_Clk и AXILite_ACLK должно быть синхронно и связан с тем же источником часов. IPCore_RESETN и AXILite_ARESETN должен быть соединен с тем же источником сброса. Смотрите Синхронизацию Глобального Сигнала Сброса к Области Часов Ядра IP.