Программное обеспечение HDL Verifier™ состоит из функций MATLAB®, Система MATLAB object™, и библиотека блоков Simulink®, все из которых устанавливают линии связи между симулятором HDL и MATLAB или Simulink.

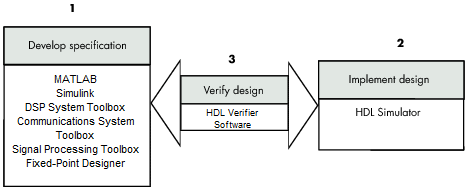

Программное обеспечение HDL Verifier оптимизировало FPGA и разработку ASIC путем интеграции инструментов, доступных для следующих процессов:

Разработка технических требований для оборудования проектирует образцы модели

Реализация оборудования проектирует в HDL на основе образца модели

Проверка проекта против исходного проекта

Следующий рисунок показывает, как симулятор HDL и продукты MathWorks® помещаются в этот аппаратный сценарий проекта.

Когда рисунок показывает, инструменты подключений программного обеспечения HDL Verifier, которые традиционно использовались дискретно, чтобы выполнить определенные шаги в процессе проектирования. Путем соединения этих инструментов ссылка упрощает верификацию путем разрешения вам cosimulate реализации и исходной спецификации непосредственно. Этот cosimulation приводит к значительной экономии времени и устранению ошибок, свойственных к ручному сравнению и контролю.

В дополнение к предыдущему сценарию проекта программное обеспечение HDL Verifier позволяет вам работать с инструментами следующими способами:

Используйте MATLAB или Simulink, чтобы создать тестовые сигналы и испытательные стенды программного обеспечения для HDL-кода

Используйте MATLAB или Simulink, чтобы обеспечить поведенческую модель для симуляции HDL

Используйте возможности анализа и визуализации MATLAB понимания в реальном времени реализации HDL

Используйте Simulink, чтобы перевести устаревшие описания HDL в представления уровня системы

Примечание

Вы можете cosimulate использование модуля SystemVerilog, SystemC или оба с MATLAB или Simulink с помощью программного обеспечения HDL Verifier. Запишите простые обертки вокруг SystemC и убедитесь, что связи SystemVerilog cosimulation являются к портам или сигналам типов данных, поддержанных ссылкой cosimulation интерфейсом.

Больше обсуждения того, как работы cosimulation могут быть найдены в следующих разделах:

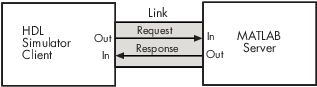

Когда соединено с MATLAB, функциями симулятора HDL как клиент, когда следующий рисунок показывает.

В этом сценарии функция сервера MATLAB ожидает запросов на обслуживание, которые это получает от сеанса симулятора HDL. После получения запроса сервер устанавливает линию связи и вызывает заданную функцию MATLAB, которая вычисляет данные для, проверяет или визуализирует модуль HDL (закодированный в VHDL® или Verilog®), который является объектом симуляции в симуляторе HDL.

После того, как сервер запускается, можно запустить и сконфигурировать симулятор HDL или использование с MATLAB с предоставленной функцией HDL Verifier:

nclaunch (Incisive®)

vsim (ModelSim®)

Следующий рисунок показывает, как функция испытательного стенда MATLAB повторяется и связывается с симулятором HDL во время сеанса симуляции испытательного стенда.

Следующий рисунок показывает, как функция компонента MATLAB переносится и связывается с симулятором HDL во время сеанса симуляции компонента.

Когда вы начинаете определенный испытательный стенд или сеанс компонента, вы задаете параметры, которые идентифицируют следующую информацию:

Режим и, если применимо, данные TCP/IP для соединения с сервером MATLAB

Функция MATLAB, которая сопоставлена с и выполняется от имени экземпляра HDL

Синхронизация технических требований и других данных об управлении, которые задают, когда функция MATLAB модуля должна быть названа

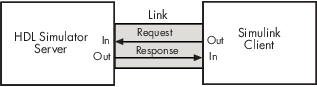

Когда соединено с Simulink, симулятор HDL функционирует как сервер как показано в следующем рисунке.

В этом случае симулятор HDL отвечает на запросы симуляции, которые он получает от блоков cosimulation в модели Simulink. Вы начинаете cosimulation сеанс с Simulink. После того, как сеанс запускается, можно использовать Simulink и симулятор HDL, чтобы контролировать прогресс симуляции и результаты. Например, вы можете добавить сигналы в окно Wave симулятора HDL, чтобы контролировать схемы синхронизации симуляции.

Используя диалоговое окно Block Parameters для блока HDL Cosimulation, можно сконфигурировать следующее:

Блокируйте порты ввода и вывода, которые соответствуют сигналам (включая внутренние сигналы) модуля HDL. Можно задать шаги расчета и типы данных с фиксированной точкой для отдельных выходных портов блока при желании.

Тип коммуникационных и коммуникационных настроек используется для обмена данными между инструментами симуляции.

Возрастающее ребро или ребро падения синхронизируют, чтобы примениться к вашему модулю. Можно индивидуально задать период каждых часов.

Команды Tcl, чтобы запуститься до и после симуляции.

Программное обеспечение HDL Verifier оборудует симулятор HDL набором индивидуально настраиваемых функций. Для ModelSim, когда вы используете функцию vsimulink, вы выполняете симулятор HDL с экземпляром модуля HDL для cosimulation с Simulink. После того, как модуль загружается, можно запустить cosimulation сеанс с Simulink. Острые пользователи могут выполнить те же операции с функцией hdlsimulink.

Программное обеспечение HDL Verifier также включает блок для генерации файлов дампа изменений значения (VCD). Можно использовать файлы VCD, сгенерированные с этим блоком, чтобы выполнить следующие задачи:

Просмотрите формы волны симуляции Simulink в своей среде симуляции HDL

Сравните результаты нескольких запусков симуляции, с помощью тех же или различных сред симуляции

Использование в качестве входа к инструментам постанализа методом моделирования

HDL Verifier содержит функцию Cosimulation Wizard, которая использует существующий HDL-код, чтобы создать индивидуально настраиваемую функцию MATLAB (испытательный стенд или компонент), Системный объект MATLAB или блок Simulink HDL Cosimulation. Для получения дополнительной информации смотрите, Готовятся Импортировать HDL-код для Cosimulation.

Режим коммуникации, которую вы используете для ссылки между симулятором HDL и MATLAB или Simulink, зависит от ли ваше выполнение приложения в локальной настройке единой системы или в конфигурации сети. Если эти продукты и Продукты Mathworks могут запуститься локально в той же системе, и ваше приложение требует только одного канала связи, у вас есть опция выбора между общей памятью и коммуникацией сокета TCP/IP. Коммуникация общей памяти обеспечивает оптимальную эффективность и является режимом по умолчанию коммуникации.

Режим сокета TCP/IP более универсален. Можно использовать его для единой системы и конфигураций сети. Эта опция предлагает самую большую масштабируемость. Для больше на коммуникации сокета TCP/IP, смотрите Порты Сокета TCP/IP.

Все функции MATLAB HDL Verifier и блок HDL Cosimulation предлагают тот же прозрачный для языка набор функций для обеих моделей Verilog и VHDL.

Программное обеспечение HDL Verifier также поддерживает модели HDL на разных языках (модели и с компонентами Verilog и с VHDL), позволяя вам cosimulate сигналам VHDL и Verilog одновременно. И MATLAB и программное обеспечение Simulink могут получить доступ к компонентам на различных языках на любом уровне.

Руководство пользователя HDL Verifier предоставляет инструкцию для использования программного обеспечения верификации с поддерживаемыми симуляторами HDL для следующих рабочих процессов:

Симуляция компонента HDL в среде испытательного стенда MATLAB

Заменяя компонент HDL на функцию компонента MATLAB

Симуляция компонента HDL в среде места размещения Simulink Test

Заменяя компонент HDL на алгоритм Simulink

Запись изменений состояния Simulink Signal для последующей обработки

| Функция продукта | Необходимые продукты | Рекомендуемые продукты | Поддерживаемые платформы |

|---|---|---|---|

| MATLAB и симулятор HDL cosimulation (функция) | MATLAB | Fixed-Point Designer™, Signal Processing Toolbox™ | Windows® 32-и 64-битный; Linux® 64-bit |

| MATLAB и симулятор HDL cosimulation (Системный объект) | MATLAB и Fixed-Point Designer | Communications Toolbox™, DSP System Toolbox™ | Windows 32-и 64-bit; 64-битный Linux |

| Simulink и симулятор HDL cosimulation | Simulink, Fixed-Point Designer | Signal Processing Toolbox, DSP System Toolbox | Windows 32-и 64-bit; 64-битный Linux |