Можно определять внутренние сигналы в модели как тестовые точки и сконфигурировать генератор SystemVerilog DPI, чтобы создать одну или несколько функций доступа. Можно также позволить войти в систему тестовые точки. Затем можно использовать сгенерированный испытательный стенд, чтобы сравнить данные Simulink® со значениями, наблюдаемыми при выполнении компонента SystemVerilog.

Выберите внутренний сигнал в своей модели, после этих инструкций:

Включите тестовую точку в источнике сигнала. Если тестовая точка находится на соединяющемся сигнале, такой, когда между подсистемами, сила сигнала оптимизирована из сгенерированного кода.

Выберите сигнал, который не является вводом или выводом вашего компонента. Если вы выбираете сигнал I/O, генератор не обеспечивает функцию доступа. Такая функция доступа избыточна, потому что у вас уже есть видимость сигналов ввода-вывода.

Комплексные сигналы не поддерживаются.

Виртуальные сигналы и шины не поддерживаются.

Непрерывные, асинхронные, и инициированные шаги расчета не поддерживаются.

Многоскоростные проекты не поддерживаются для логгирования сигнала. Можно добавить тестовую точку и сгенерировать функцию доступа. Однако испытательный стенд является одним уровнем и не может выполнить сравнение с записанными данными на различных уровнях.

Модели - ссылки не поддерживаются. Если вы хотите добавить тестовую точку в модели - ссылке, сначала необходимо соединить сигнал из модели - ссылки. Если сигнал доступен в вашей модели, можно выбрать его как тестовую точку.

В вашей модели щелкните правой кнопкой по сигналу и выберите Properties.

Установите флажок Test point.

Дайте тестовой точке уникальное имя в поле Signal name.

Опционально, выберите Log signal data. Этот флажок позволяет сгенерированному испытательному стенду выдержать сравнение, записанные данные из модели против значений наблюдали при выполнении сгенерированного компонента. Испытательный стенд использует сгенерированные функции доступа, чтобы выбрать значения сигналов во время симуляции.

Для получения дополнительной информации о тестовых точках и входящем в систему Simulink, смотрите, Конфигурируют Сигналы как Тестовые точки (Simulink).

Откройте свою модель, и на вкладке Apps, нажмите HDL Verifier. Затем на вкладке HDL Verifier нажмите C Code Settings. Диалоговое окно Configuration Parameters открывается на Code Generation.

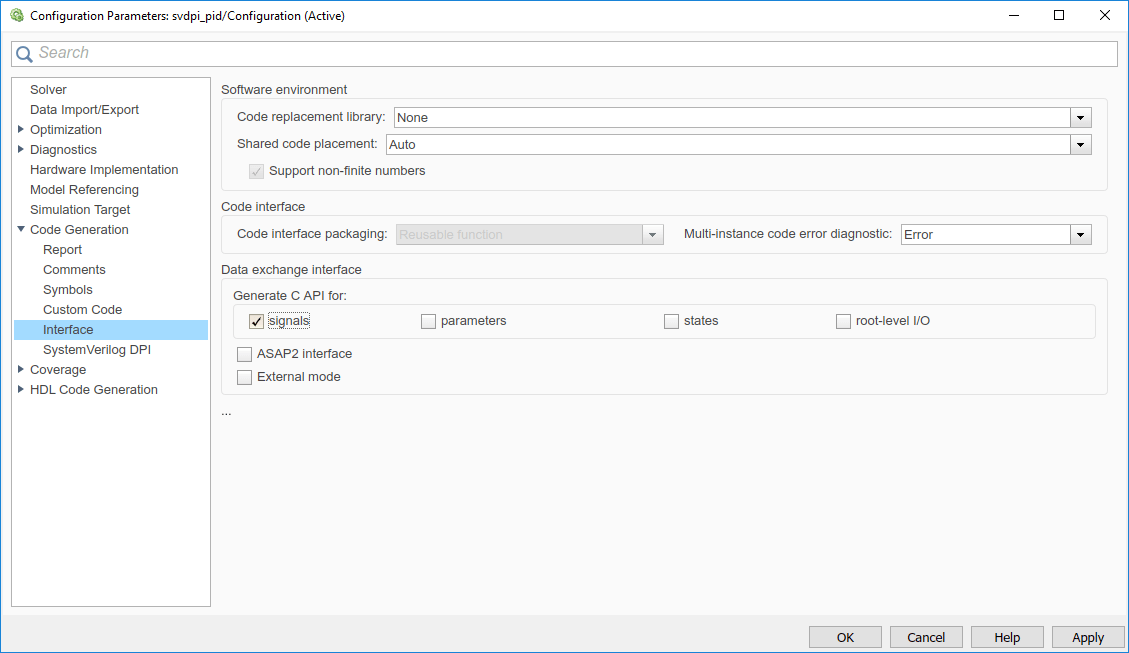

На левой панели, под Code Generation, выбирают Interface.

В Generate C API for гарантируйте, что флажок signals устанавливается. Другие флажки не влияют на DPI или испытательный стенд компонента.

Во вкладке HDL Verifier нажмите SystemVerilog Settings.

Для Generate access function to test point выберите One function per Test Point или One function for all Test Points.

Если вы выбираете One function for all Test Points, одна функция возвращает значения для всех тестовых точек.

DPI_TestPointAccessFcn(input chandle objhandle,input real Name1,inout real Name2);

Если вы выбираете One function per Test Point, каждый сигнал имеет отдельную функцию доступа.

DPI_Name_TestPoint(input chandle objhandle,inout real Name);

Если вы выбираете None, инструмент не генерирует функции доступа.