Определите частоту и основной компонент угла фазы сигнала

Simscape / Электрический / Специализированные Энергосистемы / Управление

Блок PLL моделирует Цикл блокировки фазы (PLL) система управления с обратной связью, которая отслеживает частоту и фазу синусоидального сигнала при помощи внутреннего генератора частоты. Система управления настраивает внутреннюю частоту генератора, чтобы сохранить различие в фазах для 0.

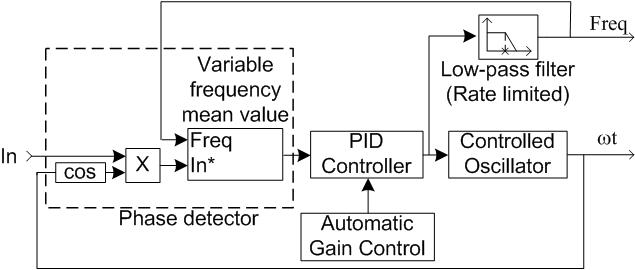

Рисунок показывает внутреннюю схему PLL.

Входной сигнал смешан с внутренним сигналом генератора. Компонент DC смешанного сигнала (пропорциональный разности фаз между этими двумя сигналами) извлечен со средним значением переменной частоты. Контроллер Пропорциональной Интегральной Производной (PID) с дополнительным автоматическим управлением усилением (AGC) сохраняет разность фаз для 0 путем действия на управляемый генератор. PID выход, соответствуя скорости вращения, отфильтрован и преобразован в частоту в герц, который используется средним значением.

Задайте минимальную ожидаемую частоту входного сигнала. Это наборы параметров buffer size блока Mean (Variable Frequency), используемого в блоке, чтобы вычислить среднее значение. Значением по умолчанию является 45.

Задайте начальную фазу и частоту входного сигнала. Значением по умолчанию является [0, 60].

Задайте пропорциональное, интеграл и производные усиления внутреннего ПИД-регулятора. Используйте усиления, чтобы настроить время отклика PLL, перерегулирование и установившуюся ошибочную эффективность. Значением по умолчанию является [180, 3200, 1].

Задайте постоянную времени для фильтра первого порядка блока производной ПИДа. Значением по умолчанию является 1e-4.

Задайте максимальный положительный и отрицательный наклон частоты сигнала. Значением по умолчанию является 12.

Укажите, что lowpass второго порядка фильтрует частоту среза. Значением по умолчанию является 25.

Задайте шаг расчета блока в секундах. Установите на 0, чтобы реализовать непрерывный блок. Значением по умолчанию является 0.

Когда этот флажок устанавливается, блок PLL оптимизирует свою эффективность путем масштабирования сигнала регулятора ПИДа согласно величине входного сигнала. Выберите эту опцию, когда входной сигнал не будет нормирован. Значение по умолчанию выбрано.

InНормированный входной сигнал, в pu.

FreqИзмеренная частота, в герц.

wtУгол (рад), варьирующийся между 0 и 2*pi, синхронизировался на пересечении нулем (повышение) основного принципа входного сигнала.

| Размер шага | Заданный в параметре Sample Time. Непрерывный, когда Sample Time = 0. |

| Скалярное расширение | Нет |

| Определенный размерность | Нет |

| Обнаружение пересечения нулем | Да |

power_PLL пример показывает использование PLL (3ph) и блоки PLL.

Блок PLL питается синусоидальным сигналом 60 Гц, увеличиваясь до 61 Гц с 0,5 с до 1,5 с. Заметьте, что частота достигает новой частоты в короткое время отклика.

Блок PLL (3ph) питается трехфазными синусоидальными сигналами, увеличивающимися от 60 Гц до 61 Гц между 0,5 и 1,5 секундами. PLL (3ph) частота достигает новой частоты быстрее, чем PLL из-за дополнительной информации о фазе.

Шаг расчета модели параметрируется с переменной Ts (со значением по умолчанию 0). Чтобы дискретизировать блок PLL, в командной строке MATLAB®, входят

Ts = 50e-6