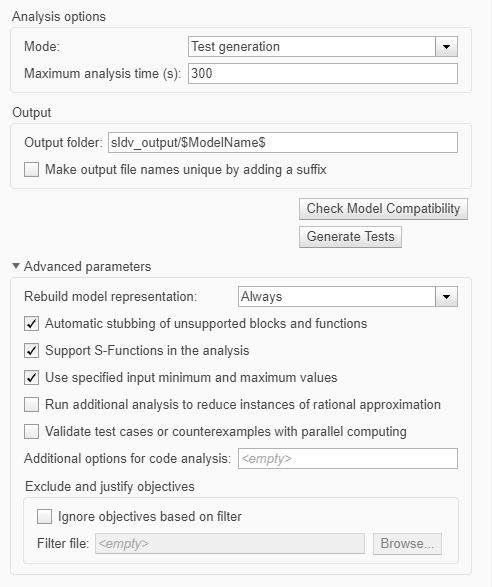

Сделайте имена выходного файла уникальными путем добавления суффикса

Сгенерируйте Тестирует/Обнаруживает Ошибочные/Доказывать Свойства

Автоматическое блокирование неподдерживаемых блоков и функций

Используйте заданный, вводит минимальные и максимальные значения

Запустите дополнительный анализ, чтобы уменьшать экземпляры рационального приближения

Подтвердите тесты или контрпримеры с параллельными вычислениями

Задайте опции анализа и сконфигурируйте Simulink® Design Verifier™ выход.

Задайте аналитический режим для Simulink Design Verifier.

Значение по умолчанию:

Test generation

Design error detectionОбнаруживает ошибки переполнения целочисленной и фиксированной точки и ошибки деления на нуль в модели

Test generationГенерирует тесты для модели.

Property provingДоказывает свойства модели.

Simulink Design Verifier задает значение этой опции, когда вы выбираете одну из этих опций анализа от вкладки Design Verifier в разделе Mode:

Выберите Design Error Detection, затем нажмите Detect Design Errors.

Выберите Test Generation, затем нажмите Generate Tests.

Выберите Property Proving, затем нажмите Prove Properties.

Когда вы устанавливаете параметр Mode, кнопка ниже Check Model Compatibility изменяется можно следующим образом:

Режим: Test generation, чтения кнопки: Generate Tests

Режим: Design error detection, чтения кнопки: Detect Errors

Режим: Property proving, чтения кнопки: Prove Properties

Параметр:

DVMode |

| Ввод: массив символов |

Значение:

'TestGeneration' | 'DesignErrorDetection' | 'PropertyProving' |

Значение по умолчанию:

'TestGeneration' |

Задайте максимальное время (в секундах), что Simulink Design Verifier тратит анализ модели. Можно установить значение максимального аналитического времени к значению, которое вы готовы ввести к анализу. Можно также остановить анализ в любое время.

Значение по умолчанию:

300

Значение, которое вы вводите, представляет максимальное количество секунд, Simulink Design Verifier анализирует вашу модель.

Параметр:

DVMaxProcessTime |

Ввод:

double |

| Значение: любое допустимое значение |

Значение по умолчанию:

300 |

Задайте путь, в который Simulink Design Verifier пишет свой выход.

Значение по умолчанию:

sldv_output/$ModelName$

Введите путь, который является или абсолютным или относительно текущей папки.

$ModelName$ лексема, которая представляет имя модели.

Можно использовать следующие параметры, чтобы настроить названия и местоположение Simulink Design Verifier выход:

На панели Results:

Data file name

Harness model file name

Simulink Test options > Test File name

На панели Report:

Report file name

File path of the output model

На панели Block Replacements:

File path of the output model

Параметр:

DVOutputDir |

| Ввод: массив символов |

| Значение: любой допустимый путь |

Значение по умолчанию:

'sldv_output/$ModelName$' |

Задайте, делает ли Simulink Design Verifier свои имена выходного файла уникальными путем добавления числового суффикса.

Значение по умолчанию: On

Добавляет инкрементный числовой суффикс к именам выходного файла Simulink Design Verifier. Выбирание этой опции препятствует тому, чтобы программное обеспечение перезаписало существующие файлы, которые имеют то же имя.

Не добавляет суффикс к именам выходного файла Simulink Design Verifier. В этом случае программное обеспечение может перезаписать существующие файлы, которые имеют то же имя.

Параметр:

DVMakeOutputFilesUnique |

| Ввод: массив символов |

Значение:

'on' | 'off' |

Значение по умолчанию:

'on' |

Осуществите проверку, чтобы оценить вашу модель для совместимости с Simulink Design Verifier. Для получения дополнительной информации смотрите Проверки Simulink Design Verifier.

Когда вы устанавливаете параметр Mode, эта кнопка изменяется можно следующим образом:

Режим: Test generation, чтения кнопки: Generate Tests

Для получения дополнительной информации смотрите то, Что Генерация Теста?.

Режим: Design error detection, чтения кнопки: Detect Errors

Для получения дополнительной информации смотрите то, Что Поиск ошибок проектирования?.

Режим: Property proving, чтения кнопки: Prove Properties

Для получения дополнительной информации смотрите то, Что Доказывает Свойство?.

Задайте, восстановить ли представление модели для анализа Simulink Design Verifier.

Значение по умолчанию:

If change is detected

AlwaysВсегда восстанавливайте представление модели.

If change is detectedВосстановите представление модели только, когда программное обеспечение обнаружит любое изменение в модели.

Параметр:

DVRebuildModelRepresentation |

Ввод:

character array |

Значение:

'Always' | 'IfChangeIsDetected' |

Значение по умолчанию:

'If change is detected' |

Задайте, проигнорировать ли неподдерживаемые блоки и функции во время анализа.

Значение по умолчанию: On

Игнорирует неподдерживаемые блоки и функции и возобновляет анализ.

Выводит предупреждение, когда Simulink Design Verifier сталкивается с неподдерживаемым блоком или функцией и спрашивает, хотите ли вы продолжить анализ.

Параметр:

DVAutomaticStubbing |

| Ввод: массив символов |

Значение:

'on' | 'off' |

Значение по умолчанию:

'on' |

Задайте, разрешить ли поддержку S-функций, которые были скомпилированы, чтобы быть совместимыми с Simulink Design Verifier.

Значение по умолчанию: On

Включает поддержку S-функций, которые были скомпилированы, чтобы быть совместимыми с Simulink Design Verifier.

Simulink Design Verifier автоматически S-функции тупиков во время анализа.

Параметр:

DVSFcnSupport |

| Ввод: массив символов |

Значение:

'on' | 'off' |

Значение по умолчанию:

'on' |

Поддержите ограничения и факторы для кода C/C++ и S-функций

Задайте, сгенерировать ли тесты, которые рассматривают заданные минимальные и максимальные значения как ограничения для всех входных сигналов в вашей модели.

Значение по умолчанию: On

Рассматривает заданные минимальные и максимальные значения как ограничения для всех входных сигналов.

Игнорирует любые заданные минимальные и максимальные значения.

Параметр:

DVDesignMinMaxConstraints |

| Ввод: массив символов |

Значение:

'on' | 'off' |

Значение по умолчанию:

'on' |

Задайте, пытается ли Simulink Design Verifier уменьшать использование рационального приближения во время анализа.

Значение по умолчанию: On

Когда вы используете Simulink Design Verifier, чтобы анализировать модели, Simulink Design Verifier пытается уменьшать использование рационального приближения если модель. Включение этой установки может увеличить аналитическое время.

Simulink Design Verifier не пытается уменьшать использование рационального приближения во время анализа.

Параметр:

DVReduceRationalApprox |

| Ввод: массив символов |

Значение:

'on' | 'off' |

Значение по умолчанию:

'on' |

Задает, подтвердить ли тесты или контрпримеры с параллельными вычислениями. Эта опция требует лицензии Parallel Computing Toolbox™.

В общем случае параллельное выполнение может помочь уменьшать время валидации если:

У вас есть комплексная модель Simulink, которая занимает много времени, чтобы симулировать.

Анализ Simulink Design Verifier превышает максимальное аналитическое время и приводит ко многим целям с состоянием Needs Simulation. Для получения дополнительной информации смотрите Удовлетворенные Цели - Симуляцию Потребностей и Сфальсифицированные Цели - Симуляция Потребностей.

Анализ генерации тестов генерирует длинные тесты. Это может быть то, потому что вы установили Test suite optimization на LongTestcases или значение Maximum test case steps больше значения по умолчанию. Для получения дополнительной информации см. Обзор Панели Генерации тестов.

Следующие моменты должны быть рассмотрены при использовании параллельных вычислений для валидации:

Запуск параллельного пула может занять время, который влияет на полное аналитическое время. Уменьшать аналитическое время:

Убедитесь, что параллельный пул уже запускается, прежде чем вы запустите анализ генерации тестов. По умолчанию параллельный пул закрывается будучи неактивным для конкретного количества минут. Чтобы изменить настройки, смотрите, что тема 'Задает Ваши Параллельные Настройки' в Parallel Computing Toolbox.

Загрузите Simulink на всех параллельных рабочих пула.

Симуляция происходит последовательно когда:

Кластером не является local. Сконфигурируйте параллельные настройки, чтобы использовать local кластер только. Чтобы изменить настройки, смотрите, что тема 'Задает Ваши Параллельные Настройки' в Parallel Computing Toolbox.

Модель находится в dirty state до запуска анализа SLDV.

Модель имеет ToFile блоки.

Модель является внутренней обвязкой.

Функции векторного произведения, такие как functional testing and coverage analysis от менеджера по Simulink Test™ не поддерживают параллельные вычисления для валидации. Для получения дополнительной информации смотрите, Выполняют Функциональное Тестирование и Анализируют Тестовое покрытие (Simulink Test).

Значение по умолчанию: Off

Если у вас есть лицензия Parallel Computing Toolbox, то Simulink Design Verifier подтверждает тесты или контрпримеры параллельно через несколько рабочих на той же машине.

Simulink Design Verifier подтверждает тесты или контрпримеры в сериале.

Параметр:

DVUseParallel |

| Ввод: массив символов |

Значение:

'on' | 'off' |

Значение по умолчанию:

'off' |

Задайте дополнительные опции для анализа S-функций, которые были скомпилированы, чтобы быть совместимыми с Simulink Design Verifier. Для получения дополнительной информации смотрите Ограничения Поддержки и Факторы для Кода C/C++ и S-функций.

Значение по умолчанию:

''

Введите дополнительные опции для анализа S-функций, которые были скомпилированы, чтобы быть совместимыми с Simulink Design Verifier. Например, чтобы задать максимальный размер массивов, введите defaultArraySize = 512.

Параметр:

DVCodeAnalysisExtraOptions |

| Ввод: массив символов |

| Значение: любая допустимая опция для анализа S-функций |

Значение по умолчанию:

'' |

Задайте, чтобы анализировать модель, игнорируя цели в Filter file. Filter file содержит цели покрытия модели для генерации тестов и цели поиска ошибок проектирования, которые вы хотите отфильтровать от анализа.

Значение по умолчанию: Off

Игнорирует цели в Filter file во время анализа поиска ошибок проектирования и генерации тестов.

Генерирует результаты для всех целей для генерации тестов и анализа поиска ошибок проектирования, включая тех в Filter file.

Этот параметр включает Filter file.

Параметр:

DVCovFilter |

| Ввод: массив символов |

Значение:

'on' | 'off' |

Значение по умолчанию:

'off' |

Фильтрация покрытия (Simulink Coverage)

Задайте папку и имя файла для файла, который содержит цели покрытия модели для генерации тестов и цели поиска ошибок проектирования, которые вы хотите отфильтровать от анализа.

Значение по умолчанию:

''

Задайте имя папки и имени файла, которое содержит цели, которые вы хотите проигнорировать от анализа поиска ошибок проектирования и генерации тестов.

Нажмите кнопку Browse, чтобы выбрать существующий Filter file.

Параметр:

DVCovFilterFileName |

| Ввод: массив символов |

| Значение: любой допустимый путь и имя файла |

Значение по умолчанию:

'' |

Правила фильтра покрытия и файлы (Simulink Coverage)

Отфильтруйте цели при помощи аналитического средства просмотра фильтра

Просмотрите к файлу, который содержит цели, которые вы хотите проигнорировать от анализа генерации тестов и поиска ошибок проектирования.

Эта кнопка включена Ignore objectives based on filter.