Шаблон RFSoC обеспечивает имитационную модель для исходного проекта SoC, доступного от Пакета Поддержки SoC Blockset™ для Устройств Xilinx®. Используйте этот шаблон, чтобы симулировать полный исходный проект. Анализируйте эффекты внутренней и внешней возможности соединения на передаче и получите коммуникационные алгоритмы, такие как поведение памяти и ввод/вывод Радиочастоты (RF) (ввод-вывод) поведение.

Чтобы начать с моделью SoC Blockset для разработки RFSoC-поддерживающей системы радиосвязи, выполните шаги в, Создают Модель SoC Используя Шаблон SoC Blockset. Затем добавьте свои алгоритмы передатчика и приемника в подсистеме FPGA и свой алгоритм процессора в подсистеме Процессора.

DSP System Toolbox™

Пакет поддержки SoC Blockset для устройств Xilinx

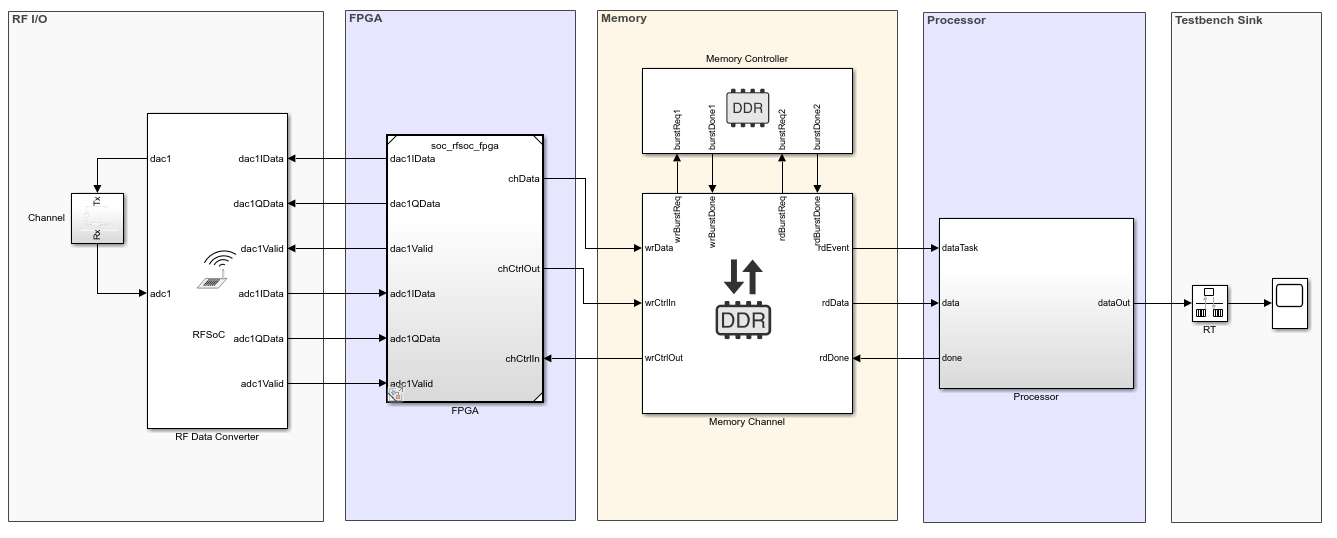

Шаблон RFSoC включает три модели: Топ-модель, модель FPGA и модель Processor. В Топ-модели блок RF Data Converter соединяется с блоком FPGA и обеспечивает интерфейс RF I/O. Блок FPGA реализует алгоритмы приемника и передатчика. Алгоритм FPGA включает блок Test Source, который генерирует синусоидальный сигнал и управляет им к цифро-аналоговому преобразователю (DAC) через подсистему Алгоритма Передатчика. Подсистема Алгоритма Передатчика реализована, когда простая передача соединяет, и подсистема Алгоритма Приемника реализована с помощью блока Gain и логики вниз-сэмплера. Регистр конфигурации SrcSelReg моделируется в FPGA, чтобы выбрать источник данных для подсистемы Алгоритма Приемника. Процессор пишет регистр SrcSelReg, чтобы выбрать или тестовый источник из FPGA или данные RF из аналого-цифрового конвертера (ADC) в блоке RF Data Converter. Данные из подсистемы FPGA передаются подсистеме Процессора через блок Memory Channel. Параметр Channel Type в блоке Memory Channel устанавливается на AXI4-Stream to software via DMA, который моделирует передачу данных прямого доступа к памяти (DMA) через разделяемую внешнюю память.

Используйте этот шаблон в качестве руководства, заменяя подсистемы Алгоритма Алгоритма и Передатчика Приемника в модели FPGA и подсистему Алгоритма Процессора в модели Processor с вашей собственной функциональностью. В этом шаблоне блок RF Data Converter сконфигурирован с интерфейсом RF 1 на 1 и цифровым интерфейсом I/Q. Номер выборок на такт определяется к 2. Путь RF в этом шаблоне циклично выполняется назад. Если вы хотите использовать различные данные для передатчика и приемника, вы можете удалить цикл назад и можете обеспечить, желал ваших входных данных к ADC.

Процессор считывает вычисленные данные из памяти и выполняет дополнительное вычисление (реализованный в шаблоне как провод передачи). Можно просмотреть результаты симуляции путем двойного клика по блоку Time Scope в подсистеме Testbench Sink.

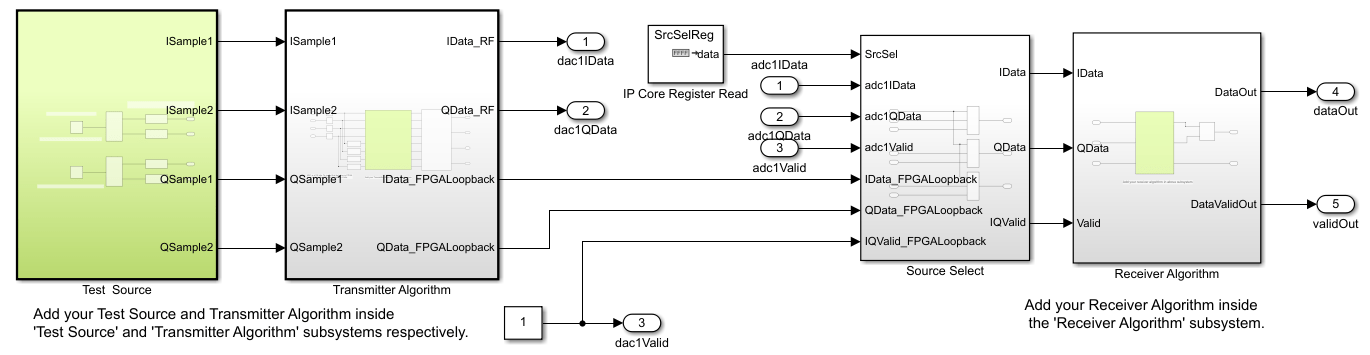

В MATLAB® Toolstrip, на вкладке Project Shortcuts , нажимают Open FPGA model. Затем откройте FPGA подсистема Обертки Tx-Rx Alg. Три области подсвечены в зеленом, как показано в этом рисунке. Эти области представляют пользовательский код и расположены в блоке Test Source, подсистеме Transmitter Algorithm и подсистеме Receiver Algorithm.

Модель FPGA включает эти разделы (подсвеченный в зеленом) для вас, чтобы изменить.

Блок Test Source – Этот блок генерирует синусоидальный сигнал на 500 кГц и управляет им к подсистеме алгоритма Передатчика. Измените тестовый источник к своим потребностям или замените его на альтернативный исходный блок.

Подсистема Алгоритма передатчика – Содержит подсистему Алгоритма Tx, подсвеченную в зеленом. Замените подсистему Алгоритма Tx на свой собственный алгоритм передатчика.

Подсистема Алгоритма приемника – Содержит подсистему Алгоритма Rx, подсвеченную в зеленом. Замените подсистему Алгоритма Rx на свой собственный алгоритм приемника.

Блоки Чтения Регистра Ядра IP – В проекте под тестом (DUT), добавляют эти блоки, чтобы добавить регистры в вашего дюйм/с алгоритма. Инициализируйте этот блок с помощью соответствующего блока Register Write в модели Processor.

Чтобы включить сопоставимое поведение симуляции, на вкладке Project Shortcuts, нажимают Open FPGA model и повторяют этот шаг.

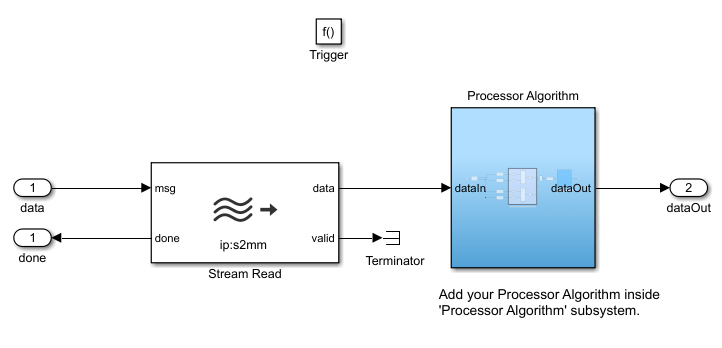

В Панели инструментов MATLAB, на вкладке Project Shortcuts , нажимают Open Processor model. Модель Processor содержит Обертку Алгоритма Процессора и Инициализировать Функциональные подсистемы. Подсистема Обертки Алгоритма Процессора подсвечена в синем, который представляет пользовательский код для алгоритма процессора. Откройте подсистему Обертки Алгоритма Процессора и замените внутреннюю подсистему Алгоритма Процессора (также подсвеченный в синем) с вашим желаемым алгоритмом. Откройте Инициализировать Функциональную подсистему и добавьте блок Register Write для каждого блока IP Core Register Read, добавленного в модели FPGA.

Используйте шаблон, чтобы создать модель SoC