Используйте шаблон Stream from Processor to FPGA, чтобы создать модель SoC Blockset™ для разработки datapath из программного обеспечения (Процессор) к оборудованию (FPGA). Чтобы создать проект с помощью шаблона Stream from Processor to FPGA, выполните шаги в, Создают Модель SoC Используя Шаблон SoC Blockset. Затем добавьте свой алгоритм FPGA в подсистеме FPGA и свой алгоритм процессора в подсистеме Процессора.

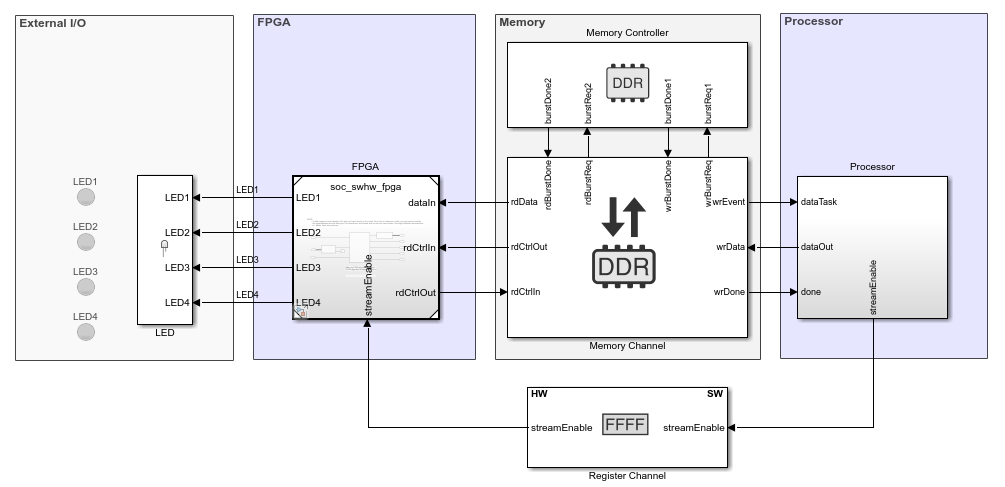

Шаблон Stream from Processor to FPGA включает три модели: Топ-модель, модель FPGA и модель Processor. Этот шаблон моделирует счетчик как источник тестовых данных и минимальную логику для алгоритмов процессора и FPGA. Используйте этот шаблон в качестве руководства, заменяя алгоритм FPGA и алгоритм процессора с вашей собственной функциональностью.

Процессор управляет сигналом выхода ready в подсистеме Обертки Алгоритма FPGA при помощи порта streamEnable. Процессор передает данные FPGA через блок Memory Channel. Параметр Channel Type в блоке Memory Channel устанавливается на Software to AXI4-Stream via DMA смоделировать передачу данных прямого доступа к памяти (DMA) через разделяемую внешнюю память.

Процессор генерирует тестовые данные и выполняет дополнительное вычисление. Дополнительный расчет реализован в шаблоне как провод передачи. Затем процессор пишет вычисленные данные в память.

В MATLAB® Toolstrip, на вкладке Project Shortcuts , нажимают Open Processor model, чтобы открыть модель процессора. В подсистеме Обертки Алгоритма Процессора две области подсвечены синие (который представляет пользовательский код), как показано в этом рисунке. Одна подсвеченная область появляется в блоке Processor Algorithm, и другая подсвеченная область появляется в блоке Test Source.

Блок Processor Algorithm – Замена внутренний блок Processor Algorithm (подсвеченный в синем) с вашим желаемым алгоритмом.

Протестируйте Исходный блок – Этот блок генерирует сигнал пандуса. Измените тестовый источник к своим потребностям или замените его на альтернативный исходный блок.

Поток Включает для блока DUT – Этот блок содержит управляющую логику, чтобы гарантировать, что память запущена, прежде чем непрерывная потоковая передача начнется. В управляющей логике сигнал streamEnable утверждается высоко только после того, как доступные буферы в канале памяти заполнены полностью.

В Панели инструментов MATLAB, на вкладке Project Shortcuts , нажимают Open FPGA model, чтобы открыть модель FPGA. В подсистеме Обертки Алгоритма FPGA блок FPGA Algorithm подсвечен зеленый (который представляет пользовательский код).

Дважды кликните подсистему Обертки Алгоритма FPGA, чтобы открыть модель. Алгоритм FPGA извлекает четыре бита из входных данных, чтобы управлять светодиодами на оборудовании. Состояние этих светодиодов указывает, что процессор пишет потоковые данные в FPGA. Замените этот блок на свой собственный алгоритм FPGA. Добавьте вводы и выводы как требуется.

Совет

Когда ваша модель FPGA будет включать больше чем один IP, задайте каждый IP как подсистему и соедините подсистемы с помощью блока Stream Connector или Video Stream Connector. Для получения дополнительной информации смотрите Факторы для Нескольких дюйм/с в Модели FPGA.

Включить сопоставимое поведение симуляции, на вкладке Project Shortcuts, вкладке Open FPGA model нажатия кнопки и повторить этот шаг.

Топ-модель шаблона включает канал регистра, чтобы связаться между процессором и моделью FPGA. Используйте канал регистра, чтобы сконфигурировать модель FPGA или считать и проверять регистры состояния. Блок Register Channel в шаблоне включает один регистр. Чтобы добавить дополнительные регистры, измените параметры блоков Register Channel, алгоритм FPGA и алгоритм процессора путем выполнения этих шагов.

Добавьте, что регистры к каналу регистра – Дважды кликают блок Register Channel, чтобы открыть маску блока и добавить дополнительные регистры по мере необходимости. Добавление регистров создает дополнительные порты на блоке Register Channel. Для получения дополнительной информации смотрите блок Register Channel.

Добавьте, что порты к модели Processor – Перешли к подсистеме Processor Algorithm Wrapper. Чтобы перейти к модели Processor, нажмите Open Processor model на вкладке Project Shortcuts. Дважды кликните подсистему Processor Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте выходной порт и логику, чтобы управлять значением к добавленному выходному порту. Для регистров чтения добавьте входной порт и логику, чтобы обработать информацию, возвращенную в регистр чтения. От топ-модели соедините порт с блоком Register Channel.

Добавьте, что порты к модели FPGA – Перешли к подсистеме FPGA Algorithm Wrapper. Чтобы перейти к модели FPGA, нажмите Open FPGA model на вкладке Project Shortcuts. Дважды кликните подсистему FPGA Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте входной порт и логику, чтобы обработать информацию, возвращенную в регистр чтения. Для регистров чтения добавьте выходной порт и логику, чтобы управлять значением к добавленному выходному порту.

От топ-модели соедините новый порт с блоком Register Channel .

Используйте шаблон, чтобы создать модель SoC