Буферный входной поток, чтобы создать линии изображений, которые имеют непрерывные допустимые пиксели

Vision HDL Toolbox / Утилиты

Хранилища блока Pixel Stream FIFO, поступающие допустимые пиксели и сопроводительные управляющие сигналы и, возвращают тот же пиксельный поток без разрывов между допустимыми пикселями каждой линии. Блок сохраняет общий размер линии и общий формат кадра видеопотока, включая недопустимые циклы.

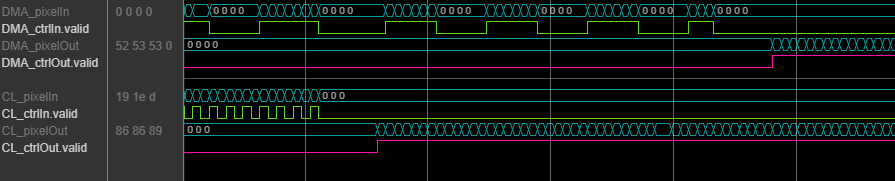

Используйте блок Pixel Stream FIFO, чтобы буферизовать источники видеосигнала. Форма волны показывает источник видеосигнала прямого доступа к памяти (DMA), где пиксели читаются в пакетах и источнике видеосигнала Camera Link®, где пиксели допустимы каждый второй такт. Создать непрерывные видео линии, Pixel Stream FIFO буфера блоков входные пиксели и управляющие сигналы каждого источника.

Этот блок использует пиксельный интерфейс потоковой передачи с шиной для сигналов управления кадром. Этот интерфейс позволяет блоку действовать независимо от размера изображения и формата. Порты pixel на этом блоке поддерживают одну пиксельную потоковую передачу или мультипиксельную потоковую передачу. Одна пиксельная потоковая передача принимает и возвращает одно пиксельное значение каждый такт. Мультипиксельная потоковая передача принимает и возвращает 4 или 8 пикселей за такт, чтобы поддержать высокую частоту кадров или форматы с высоким разрешением. Наряду с пикселем, блок принимает и возвращает pixelcontrol соедините шиной, который содержит пять управляющих сигналов. Управляющие сигналы указывают на валидность каждого пикселя и их местоположения в системе координат. Для мультипиксельной потоковой передачи один набор управляющих сигналов применяется ко всем четырем или восьми пикселям в векторе. Чтобы преобразовать систему координат (пиксельная матрица) в последовательный пиксельный поток и управляющие сигналы, используйте блок Frame To Pixels. Для полного описания интерфейса смотрите Пиксельный Интерфейс Потоковой передачи.

Этот блок также поддерживает многокомпонентные мультипикселем потоки, где пиксельный вход является матрицей значений M на n, где M является количеством пикселей, и N является количеством компонентов. Эти значения соответствуют Number of pixels и параметрам Number of components блока Frame To Pixels.

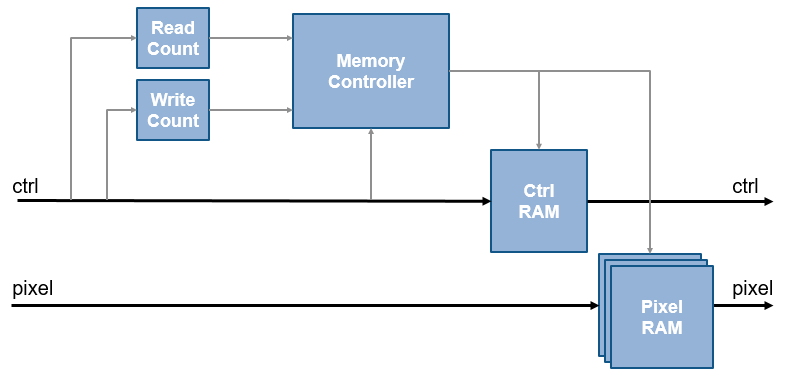

Блок Pixel Stream FIFO содержит контроллер памяти, считайте и запишите счетчики и две RAM. Один RAM хранит входящие управляющие сигналы и другие хранилища входящий пиксельный поток. Блок хранит допустимые пиксели и их сопроводительные управляющие сигналы для каждой линии, как определено входом ctrl.hStart и ctrl.hEnd сигналы. Буферизация удаляет любое пульсирующее поведение входного потока. Если сплошная линия допустимых пикселей хранится, блок возвращает новую непрерывную версию линии.

Когда вход pixel является вектором или матрицей, блок реплицирует Пиксель RAM для каждого элемента. Схема показывает RAM на Три пикселя, чтобы представлять трехкомпонентный пиксельный поток. Для мультипиксельной потоковой передачи блок настраивает buffer size линии, чтобы сохранить 1/Number of pixels пиксели. Например, с 4 3 входным потоком, каждый буферная память ¼ из пикселей для линии, таким образом, существуют RAM на 12 пикселей, каждый с 2m-2 местоположения.