Можно использовать Пакет Поддержки Vision HDL Toolbox™ для Оборудования Xilinx® Zynq®-Based, чтобы моделировать алгоритмы визуализации для находящегося в Zynq оборудования, которое соединяется с действительными видеоустройствами ввода и вывода. Используйте пакет поддержки для:

Запишите видео ввода или вывода от платы и импортируйте его в Simulink® для разработки алгоритмов и верификации.

Сгенерируйте и разверните ядра IP видения в FPGA на плате. (требует HDL Coder™),

Сгенерируйте и разверните код С в процессор ARM® на плате. Можно направить видеоданные от FPGA в процессор ARM®, чтобы разработать алгоритмы обработки видеоданных, предназначенные к процессору ARM. (требует Embedded Coder®),

Просмотрите вывод своего алгоритма на устройстве HDMI.

Используя этот пакет поддержки, можно записать живое видео от устройства Zynq и импортировать его в Simulink. Источник видеосигнала может быть вводом видео HDMI к плате, тестовый генератор шаблона на чипе, включенный с исходным проектом или выходом вашего пользовательского алгоритма на плате. Можно выбрать цветовое пространство и разрешение входных кадров. Разрешение получения должно совпадать с разрешением вашей входной камеры.

Если у вас есть видеокадры в Simulink, вы можете:

Спроектируйте основанные на системе координат алгоритмы обработки видеоданных, которые работают с живым вводом данных. Используйте блоки из библиотек Computer Vision Toolbox™, чтобы быстро разработать основанные на системе координат, алгоритмы с плавающей точкой.

Используйте блок Frame To Pixels из Vision HDL Toolbox, чтобы преобразовать вход в пиксельный поток. Спроектируйте и проверьте передающие потоком пиксель алгоритмы с помощью других блоков из библиотек Vision HDL Toolbox.

Пакет Поддержки Vision HDL Toolbox для Xilinx Находящееся в Zynq Оборудование обеспечивает исходный проект для прототипирования видео алгоритмов на платах Zynq.

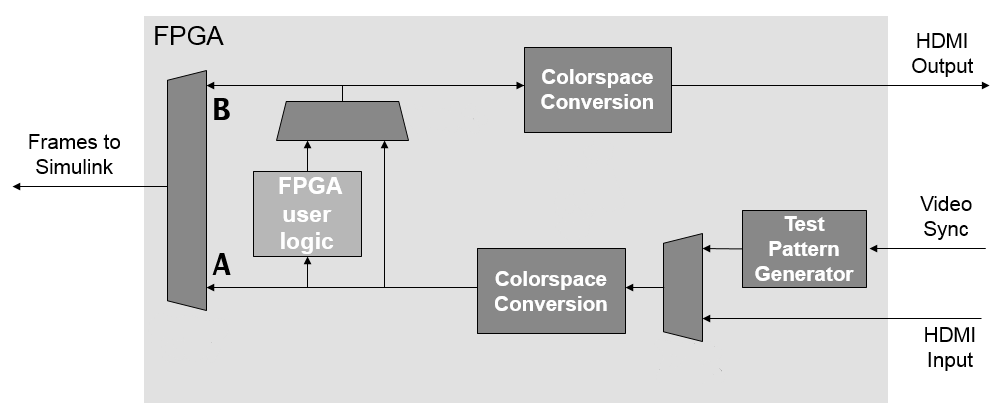

Когда вы генерируете ядро IP HDL для своего передающего потоком пиксель проекта с помощью HDL Workflow Advisor, ядро включено в этот исходный проект как раздел FPGA user logic. Точки A и B в схеме показывают варианты для того, чтобы записать видео в Simulink.

Пользовательская логика FPGA может также содержать дополнительный интерфейс к внешней памяти кадрового буфера, которую не показывают в схеме.

Примечание

Исходный проект на устройстве Zynq требует того же разрешения видео и цветного формата для целого информационного канала. Разрешение, которое вы выбираете, должно совпадать с разрешением вашего входа камеры. Проект, для которого вы предназначаетесь к пользовательскому разделу логики FPGA, не должен изменять формат кадра или цветовое пространство видеопотока.

Исходный проект не поддерживает мультипиксельную потоковую передачу.

Путем выполнения всех или части передающего потоком пиксель проекта на оборудовании, вы ускоряете симуляцию своей системы обработки видеоданных и можете проверить ее поведение на действительном оборудовании. Чтобы сгенерировать HDL-код и развернуть ваш проект в FPGA, у вас должны быть HDL Coder и Пакет Поддержки HDL Coder для Платформы Xilinx Zynq, а также Xilinx Vivado® и SDK Xilinx.

После предназначения FPGA можно получить живые выходные системы координат от пользовательской логики FPGA назад к Simulink для последующей обработки и анализа. Можно также просмотреть вывод на HDMI выход, соединенный с платой. Используя сгенерированный hardware interface model, можно управлять опциями видеосъемки и считать и записать порты AXI-Lite по пользовательской логике FPGA от Simulink в процессе моделирования.

Шаг предназначения FPGA также генерирует software interface model. Эта модель поддерживает предназначение программного обеспечения к оборудованию Zynq, включая режим external mode, процессор в цикле и полноценное развертывание. Это обеспечивает управление информационным каналом и интерфейс к любым портам AXI-Lite, которые вы задали на предназначенной подсистеме своего FPGA. Из этой модели можно сгенерировать код ARM, который управляет или отвечает на порты AXI-Lite по пользовательской логике FPGA. Можно затем развернуть код по плате, чтобы запуститься наряду с пользовательской логикой FPGA. Чтобы развернуть программное обеспечение в процессор ARM, у вас должны быть Embedded Coder и Пакет Поддержки Embedded Coder для Платформы Xilinx Zynq.