(Удалено) FFT - оптимизировано для генерации кода HDL с использованием минимальных аппаратных ресурсов

Блок БПФ минимального ресурса HDL удален. Используйте блок FFT HDL Optimized с параметром Architecture, равным Burst Radix 2, вместо этого. Дополнительные сведения см. в разделе Реализация FFT для FPGA с использованием блока, оптимизированного для FFT HDL.

Устаревший

dspobs

Блок БПФ минимального ресурса HDL реализует архитектуру БПФ, использующую минимальные аппаратные ресурсы. Блок БПФ минимального ресурса HDL поддерживает Radix-2 с алгоритмом прореживания во времени (DIT) для вычисления БПФ. Дополнительные сведения об этом алгоритме см. в блоке FFT.

Результаты, возвращаемые блоком БПФ минимального ресурса HDL, являются битово-битовыми совместимыми с результатами, возвращаемыми блоком БПФ. Работа блока БПФ минимального ресурса HDL отличается от блока БПФ из-за требований реализации аппаратных средств. Блок БПФ минимального ресурса HDL:

Требуется последовательный ввод

Генерирует последовательный выход

Работает в пакетном режиме ввода-вывода

Блок БПФ минимального ресурса HDL обеспечивает сигналы квитирования для поддержки этих функций.

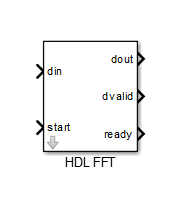

Входными портами являются:

din: Входной сигнал данных. Необходим сложный сигнал.

start: Логический управляющий сигнал. Когда этот сигнал утверждается истинным (1), блок БПФ минимального ресурса HDL инициирует обработку кадра данных.

Выходные порты:

doutВыходной сигнал данных. Алгоритм Radix-2 с DIT выдает выходные данные с линейным упорядочением.

dvalid: Логический управляющий сигнал. Блок БПФ минимального ресурса HDL утверждает этот сигнал истинным (1), когда пакет допустимых выходных данных доступен в dout порт.

ready: Логический управляющий сигнал. Блок БПФ минимального ресурса HDL утверждает этот сигнал истинным (1), чтобы указать, что он готов к обработке нового кадра.

Для эффективного аппаратного развертывания блока БПФ минимального ресурса ЛПВП необходимо тщательно рассмотреть синхронизацию потоков входных и выходных данных блока. На следующем рисунке показаны отношения синхронизации между системным синхросигналом и start, ready, и dvalid сигналы.

Когда ready утверждается, start сигнал (активный высокий) запускает блок. Высокий период цикла start сигнал не влияет на поведение блока.

Один тактовый цикл после start триггер, блок начинает загружать данные и ready сигнал отклоняется. В течение интервала, когда блок загружает, обрабатывает и выводит данные, ready низкий, и start сигнал игнорируется.

dvalid сигнал устанавливается высоким для N тактовых циклов (где N - длина БПФ) после завершения обработки. ready снова устанавливается после того, как N-точечные выходы БПФ посылаются.

Выражение Tcycle обозначает общее количество тактовых циклов, требуемых блоком БПФ минимального ресурса ЛПВП для завершения БПФ длиной N. Tcycle определяется следующим образом:

Где N > 8

Tcycle = 3N/2-2 + log2(N)*(N/2+3);

Где N = 8

Tcycle = 3N/2-1 +log2(N)*(N/2+3);

Данный Tcycle, затем можно определить период между утверждениями минимального ресурса БПФ ЛПВП start сигнал таким образом, который подходит для вашего приложения. Например:

if (N<=8)

startLen = (ceil(Tcycle/N)+1)*N;

else

startLen = ceil(Tcycle/N)*N;

endИспользовать это startLen переменная как период генератора импульсов, который управляет блоком БПФ минимального ресурса ЛПВП start вход.

Блок БПФ минимального ресурса HDL утверждает и отменяет ready и dvalid сигналы автоматически. Направляйте эти сигналы в части конструкции, которые записывают и считывают из блока БПФ минимального ресурса HDL.

Длина БПФ

По умолчанию: 8

Длина БПФ должна быть мощностью 2, в диапазоне 23.. 216.

Режим округления

По умолчанию: Floor

Блок БПФ минимального ресурса HDL поддерживает все режимы округления блока БПФ. См. также раздел вхождения блока БПФ.

Режим переполнения

По умолчанию: Saturate

Блок БПФ минимального ресурса HDL поддерживает все режимы переполнения блока БПФ. См. также раздел вхождения блока БПФ.

Таблица синусов

По умолчанию: Same word length as input

Выберите способ указания длины слова для значений таблицы синусов. Длина дроби значений таблицы синусов равна длине слова минус один.

При выборе Same word length as inputдлина слова значений синусоидальной таблицы соответствует длине слова, введенного в блок.

При выборе Specify word length, можно ввести длину слова для значений таблицы синусов в битах в поле Длина слова таблицы синусов. Значения таблицы синусов не соответствуют параметрам режима округления и режима переполнения; они всегда насыщаются и округляются до Nearest.

Выход продукта

По умолчанию: Same as input

Используйте этот параметр, чтобы указать, как следует обозначать выходные слова продукта и длины дробей:

При выборе Same as input, эти характеристики соответствуют характеристикам входа в блок.

При выборе Binary point scalingв полях Длина слова изделия и Длина дроби изделия можно ввести длину слова и длину дроби произведения в битах.

Аккумулятор

По умолчанию: Same as input

Используйте этот параметр, чтобы указать, как следует обозначать длины слов и дробей в накопителе:

При выборе Same as product output, эти характеристики соответствуют характеристикам продукта.

При выборе Same as input, эти характеристики соответствуют характеристикам входа в блок.

При выборе Binary point scaling, можно ввести длину слова и длину дроби накопителя в битах в полях Длина слова накопителя и Длина дроби накопителя.

Продукция

По умолчанию: Same as input

Выберите способ задания длины выходного слова и длины дроби:

При выборе Same as input, эти характеристики соответствуют характеристикам входа в блок.

При выборе Binary point scalingв полях Длина слова вывода и Длина дроби вывода (в битах) можно ввести длину слова и длину дроби вывода.

Примечание

Блок БПФ ЛПВП пропускает операцию деления на два на выходах бабочек для сигналов с фиксированной точкой.

HDL Coder™ предоставляет дополнительные опции конфигурации, которые влияют на реализацию HDL и синтезированную логику.

Этот блок имеет единую архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках проекта. Распределенная конвейерная обработка не перераспределяет эти регистры. Значение по умолчанию: |

| InputPipeline | Количество входных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

| OutputPipeline | Количество выходных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |