Развертывание алгоритмических моделей на аппаратном обеспечении FPGA позволяет проводить эфирное тестирование и проверку. Однако проектирование систем беспроводной связи для аппаратных средств требует конструктивных компромиссов между аппаратными ресурсами и пропускной способностью. Вы можете ускорить дизайн аппаратных средств и развертывание при помощи HDL-оптимизированных блоков, у которых есть подходящие для аппаратных средств интерфейсы и архитектура, приложения ссылки, которые осуществляют части LTE и 5G НОМЕР физического слоя и автоматической генерации объектного кода HDL. Вы также можете использовать пакеты поддержки оборудования, чтобы помочь в развертывании и проверке конструкции на реальном оборудовании.

Продукты MathWorks ® HDL, такие как Wireless HDL Toolbox™, позволяют начать с математической модели, такой как MATLAB ® code от LTE Toolbox™ или 5G Toolbox™, и разработать аппаратную реализацию этого алгоритма, которая подходит для FPGA и ASIC.

Проектирование беспроводной связи часто начинается с разработки алгоритма и тестирования с использованием функций MATLAB. Код MATLAB, который обычно работает на матрицах данных с плавающей запятой, хорош для разработки математических алгоритмов, манипулирования большими наборами данных и визуализации данных.

Инженеры по аппаратным средствам обычно получают математическую спецификацию от группы алгоритмов и повторно реализуют алгоритм для аппаратных средств. Аппаратные решения требуют компромисса в использовании ресурсов для тактовой частоты и общей пропускной способности. Обычно этот компромисс означает работу с потоковыми данными и использование некоторой логики для управления хранением и потоком данных. Аппаратные инженеры обычно работают на языках описания оборудования (HDL), таких как VHDL и Verilog, которые обеспечивают циклическое моделирование и параллелизм.

Чтобы преодолеть этот разрыв между математическим алгоритмом и реализацией аппаратного обеспечения, используйте модель алгоритма MATLAB в качестве отправной точки для реализации аппаратного обеспечения. Внесите инкрементные изменения в конструкцию, чтобы сделать ее подходящей для оборудования, и перейдите к модели Simulink ®, которую можно использовать для автоматического создания кода HDL с помощью Coder™ HDL.

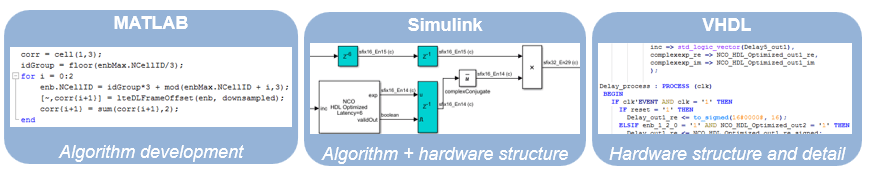

На этой диаграмме показан переход от математического алгоритма в MATLAB к аппаратно совместимой реализации в Simulink, а затем генерируемый код VHDL.

Несмотря на то, что MATLAB и Simulink поддерживают автоматическое создание кода HDL, необходимо разработать проект с учетом требований к оборудованию, и Simulink лучше подходит для моделирования оборудования на основе циклов. Он может представлять параллельные пути передачи данных и потоковые данные с управляющими сигналами для управления синхронизацией потока данных. Чтобы помочь в выборе типа с фиксированной точкой, он четко визуализирует распространение типа данных в конструкции. Это также позволяет легко конвейерировать математические операции для улучшения максимальной тактовой частоты в аппаратном обеспечении.

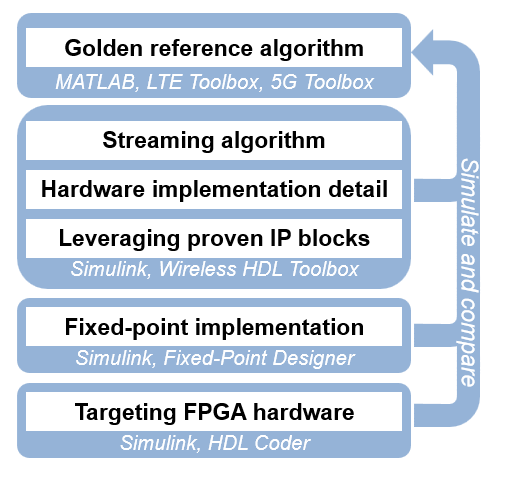

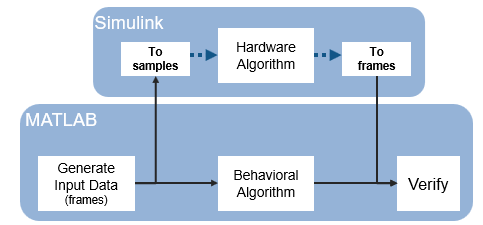

При создании аппаратно готовой конструкции используйте алгоритм MATLAB в качестве «золотой ссылки», чтобы убедиться, что каждая версия конструкции по-прежнему соответствует математическим требованиям. Рабочий процесс, показанный на схеме, использует MATLAB и Simulink в качестве инструментов совместной работы и обмена данными между алгоритмом и группами разработчиков оборудования.

Например, при разработке стандартов LTE или 5G беспроводной связи можно использовать функции LTE Toolbox и 5G Toolbox для создания золотой ссылки в MATLAB. Затем перейдите на Simulink и создайте аппаратно совместимую реализацию, используя блоки библиотеки из Wireless HDL Toolbox и блоки из Communications Toolbox™ и DSP System Toolbox™, которые поддерживают генерацию кода HDL. Можно повторно использовать инфраструктуру тестирования и генерации данных из MATLAB, импортируя данные из MATLAB в модель Simulink и возвращая выходные данные модели в MATLAB для проверки их соответствия «золотой ссылке».

Библиотечные блоки из беспроводной панели инструментов HDL реализуют кодеры, декодеры, модуляторы, демодуляторы и генераторы последовательностей для использования в LTE, 5G или общей системе беспроводной связи. В этих блоках используется стандартный интерфейс потоковых данных для аппаратных средств. Этот интерфейс упрощает соединение частей алгоритма вместе и включает управляющие сигналы, которые управляют потоком данных и отмечают границы кадра. Эти блоки поддерживают автоматическое формирование кода HDL с помощью кодера HDL. Также можно использовать блоки из Communications Toolbox и DSP System Toolbox, которые поддерживают генерацию кода HDL.

Блоки обеспечивают аппаратно подходящие архитектуры, которые оптимизируют использование ресурсов, такие как добавление сумматора и конвейера умножителя, чтобы хорошо вписаться в фрагменты DSP FPGA. Они также поддерживают автоматические и настраиваемые типы данных с фиксированной точкой. Использование стандартных блоков также позволяет использовать различные конфигурации параметров без изменения остальной части конструкции.

Список блоков, поддерживающих генерацию кода HDL, см. в разделах Список блоков панели инструментов HDL (генерация кода HDL), Список блоков панели инструментов HDL (генерация кода HDL) и Список блоков панели системных инструментов DSP (генерация кода HDL).

Беспроводной Комплект инструментов HDL обеспечивает приложения ссылки, которые содержат готовые к аппаратным средствам внедрения значительных частей LTE и 5G НОМЕР физического слоя. Эти конструкции проверяются на соответствие «золотым эталонным» функциям, предоставляемым LTE Toolbox и 5G Toolbox. Они также были протестированы на платах FPGA для подтверждения того, что они кодируют и декодируют эфирные сигналы и используют разумное количество аппаратных ресурсов. Они спроектированы как модульные, масштабируемые и расширяемые, что позволяет вставлять дополнительные физические каналы. Конструкция приемника была испытана с использованием сигналов, захваченных вне воздуха.

Набор справочных приложений включает в себя:

LTE и 5G НОМЕР основного и вторичного сигнала синхронизации (PSS/SSS) поколение и обнаружение

Генерация и восстановление детектора общего канала управления LTE нисходящей линии связи и главного информационного блока (MIB)

Декодер первого системного информационного блока (SIB1) LTE

Аппаратно-программные модели интерфейсов для разбора MIB и SIB1 битов и индексирования данных оценки канала

Генерация сигнала LTE для многоантенной передачи

Поддержка FDD и TDD для передатчиков и приемников LTE

Эти справочные приложения могут использоваться как есть для доставки пакетной информации в уникальное приложение и для создания синтезируемых VHDL или Verilog с кодером HDL. Они также служат примерами для иллюстрации рекомендуемых методов реализации алгоритмов связи на аппаратных средствах FPGA или ASIC.

Wireless HDL Toolbox предоставляет блоки, поддерживающие генерацию кода HDL. Для создания кода HDL из проектов, использующих эти блоки, необходимо иметь лицензию HDL Coder. HDL Coder производит независимый от устройства код с названиями сигналов, которые соответствуют модели Simulink. HDL Coder также предоставляет инструмент для управления процессом синтеза и таргетинга FPGA и позволяет создавать сценарии и тестовые стенды для использования с сторонними имитаторами HDL.

Чтобы помочь с настройкой и таргетингом программируемой логики на плате-прототипе, а также с проверкой конструкции системы беспроводной связи на аппаратном обеспечении, загрузите пакет аппаратной поддержки, такой как Communications Toolbox Support Package for Xilinx ® Zynq ® - Based Radio.