С помощью Simulink ® Design Verifier™ можно создавать тестовые примеры для охвата модели и пользовательских целей. Можно также измерить охват существующих тестовых случаев на основе требований и расширить эти тестовые случаи для увеличения охвата или достижения полного охвата.

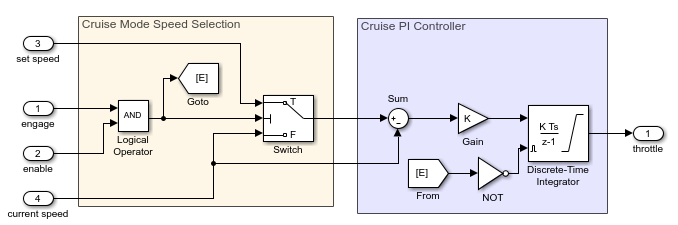

В этом учебном пособии описывается упрощенная модель круиз-контроля, которая управляет скоростью дроссельной заслонки. Создаются тестовые примеры, удовлетворяющие требованиям условий и модели принятия решений, а затем моделируются эти тестовые примеры для создания отчета о покрытии модели.

Рассмотрим упрощенную модель круиз-контроля, которая регулирует дроссель для поддержания постоянной скорости в соответствии с заданной скоростью.

Данная модель круиз-контроля отвечает следующим требованиям:

Система управления включается, когда engage и enable сигналы true. Это условие определяется блоком И.

Когда система активирована, блок Switch проходит set speed к контроллеру PI. Контроллер PI вычисляет throttle интегрированием члена ошибки, определяемого разницей set speed - current speed.

Throttle продолжает увеличиваться или уменьшаться до set speed выше или ниже, чем current speed.

Когда система не активирована, блок интегратора дискретного времени сбрасывается. Термин ошибки: zero, что означает throttle находится в положении сброса.

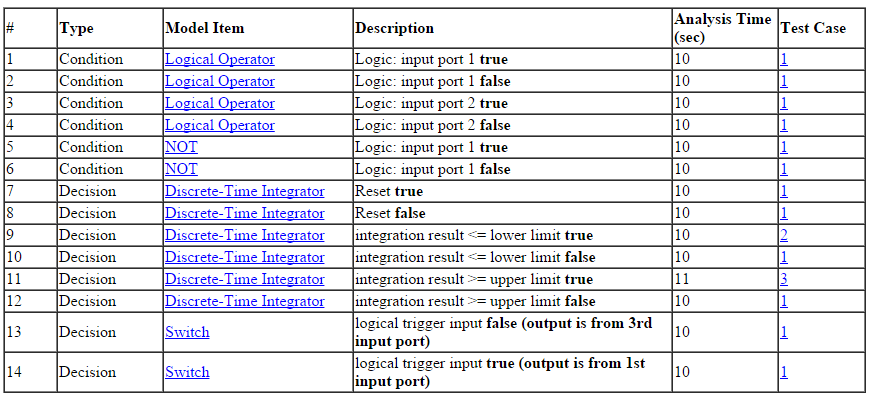

При выполнении анализа генерации теста Simulink Design Verifier генерирует тестовые примеры для целей покрытия модели, связанных с каждым элементом модели в модели. В таблице перечислены условия и цели покрытия решений для связанных блоков модели. Дополнительные сведения о целях покрытия модели см. в разделах Цели покрытия модели для генерации тестов и Объекты модели, получающие покрытие (покрытие Simulink).

| Блок | Цель покрытия модели | Описание сгенерированного тестового случая |

|---|---|---|

| И | Состояние | Каждому входному значению независимо присваивается значение true или false. |

| НЕТ | Состояние | Значение ввода равно true или false независимо. |

| Выключатель | Решение | Тест показывает, что коммутатор передает оба входных сигнала на выход. |

| Интегратор дискретного времени | Решение |

|

Результаты анализа дают подробное описание целей покрытия для каждого элемента модели и генерируют тестовые примеры для всех удовлетворенных целей. Для измерения покрытия модели моделируются созданные контрольные примеры.

Откройте модель sldvexSimpleCrureControl.

На вкладке Design Verifier в разделе Mode выберите Test Generation.

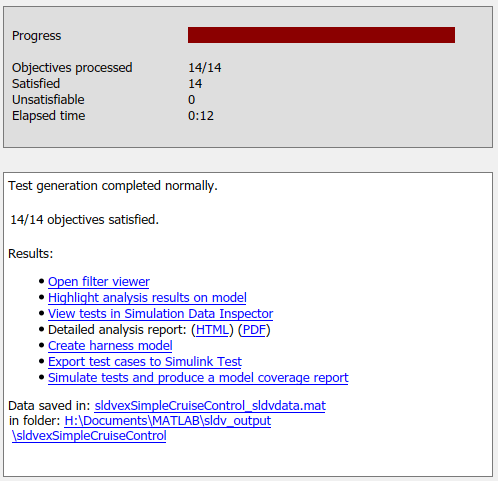

Чтобы создать тестовые примеры, щелкните Создать тесты (Generate Tests).

Результаты отображаются в окне Сводка результатов (Results Summary). Результат показывает, что все 14 цели satisfied.

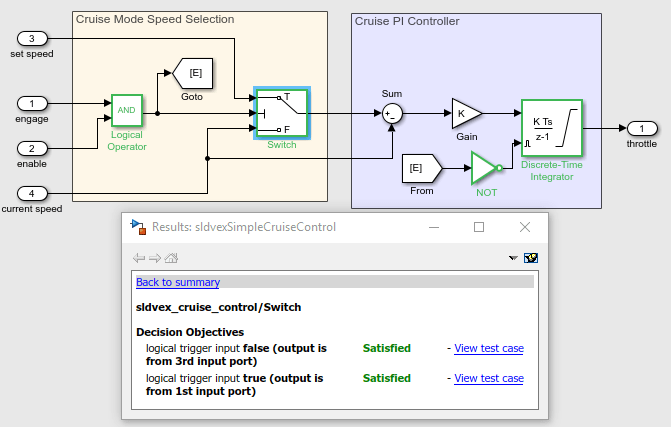

На вкладке Проверка конструкции (Design Verifier) в галерее Результаты проверки (Review Results) щелкните Выделить в модели (Highlight in Model). Цели модели, которые было установлено, что программное обеспечение выполнено, выделены зеленым цветом.

Щелкните на блоке «Переключение». В окне Инспектор результатов (Result Inspector) отображается сводка удовлетворенных целей решения.

Сводка показывает, что все цели блока Switch выполнены.

Чтобы просмотреть HTML-отчет, в коллекции «Результаты проверки» щелкните HTML-отчет.

Раздел «Статус цели теста» содержит подробное описание удовлетворенных целей для каждого элемента модели и сгенерированного тестового случая.

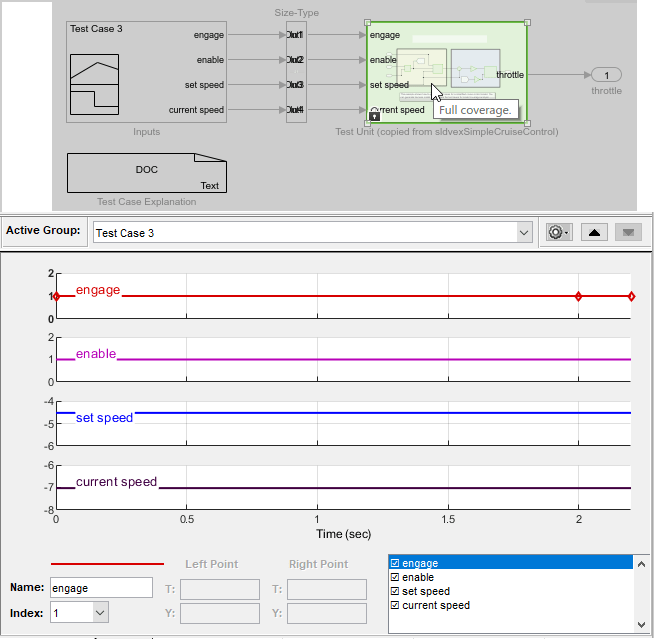

Чтобы просмотреть тестовый случай для цели покрытия модели, в окне Инспектор результатов (Result Inspector) щелкните Просмотр тестового случая (View test case). Откроется модель электрического жгута и блок Построитель сигналов (Signal Builder).

Для моделирования тестового случая в блоке Signal Builder нажмите![]() кнопку.

кнопку.

Программа моделирует тестовый пример и выделяет модель электрического жгута. Чтобы просмотреть охват элементов модели, наведите курсор на каждый объект модели в модели кабельных трасс.

Панель проверки проекта: Создание теста | Главы о состоянии целей