Если имеется большая модель, которая замедляет анализ или имеет недостижимые цели, возможно, потребуется проанализировать атомарные подсистемы или атомные подшаблоны Stateflow ® с помощью Simulink ® Design Verifier™. Этот метод позволяет реализовать восходящий подход к анализу большой модели, как описано в разделе Восходящий подход к анализу модели.

При анализе подсистемы или атомарной подшаги программное обеспечение:

Извлекает подсистему или вложенную диаграмму в новую модель.

При необходимости добавляет в созданную модель блоки, которые реплицируют контекст выполнения подсистемы или вложенной диаграммы в родительской модели.

Анализ извлеченной модели и получение результатов.

Примечание

Программное обеспечение Simulink Design Verifier может анализировать только атомарные подсистемы и атомарные подшаблоны.

Дополнительные сведения об анализе подсистем см. в разделе Создание тестовых примеров для подсистемы.

Дополнительные сведения об анализе атомных подшаблонов см. в разделе Анализ атомарного подшаблона потока состояний.

sldvextract функция позволяет извлекать подсистемы и атомарные подсхемы для проверки компонентов. Извлекая подсистему или атомарную вложенную диаграмму, можно проверить компонент в отрыве от остальной части системы, что позволяет протестировать алгоритм компонента. Дополнительные сведения см. в разделе Что такое проверка компонентов? и функции для проверки компонентов.

При анализе подсистемы или атомарного подшаблона Simulink Design Verifier создает новую модель, содержащую подсистему или атомарный подшаг, а также все входные и выходные порты, соответствующие портам, подключенным к исходной подсистеме.

Программное обеспечение присваивает портам в новой модели следующие свойства, определяемые компиляцией исходной модели:

Типы данных

Показатели выборки

Размеры сигнала

Минимальное и максимальное значения диапазонов сигналов

Программа называет новую модель subsystem_name, где subsystem_name - имя подсистемы.

В следующих разделах приведены примеры извлечения и анализа подсистем в Simulink Design Verifier.

Хранилище данных - это хранилище, в которое можно записывать данные и из которого можно считывать данные без необходимости подключения входного или выходного сигнала непосредственно к хранилищу данных.

Хранилище данных создается с помощью блока памяти хранилища данных или Simulink.Signal объект. Блок памяти хранилища данных или Simulink.Signal объект представляет хранилище данных и задает его свойства. Каждое хранилище данных должно иметь уникальное имя.

При анализе подсистемы, считывающей данные из хранилища данных, доступ к которому осуществляется вне подсистемы, выполняется следующий анализ:

Добавление блока памяти хранилища данных в новую модель.

Добавляет входной порт для записи в хранилище данных. Поскольку входные данные записываются в хранилище данных, они могут иметь любые значения (в пределах указанного типа данных) для анализа Simulink Design Verifier.

Если хранилище данных определяет минимальное и максимальное значения, эти значения назначаются новому входному порту.

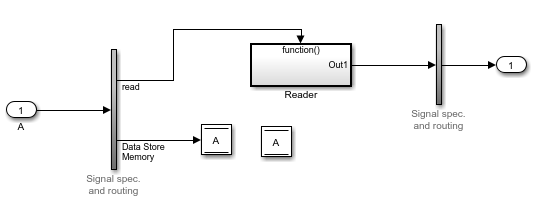

В следующем примере анализируется подсистема в sl_subsys_fcncall8 пример модели:

Откройте окно sl_subsys_fcncall8 пример модели:

Эта модель определяет хранилище данных A, из которого атомарная подсистема Reader считывает данные с помощью блока чтения хранилища данных.

Щелкните правой кнопкой мыши подсистему Reader и выберите Design Verifier > Generate Tests for Subsystem.

Окно журнала Simulink Design Verifier показывает, что программное обеспечение извлекает подсистему в новую модель с именем Reader, анализирует извлеченную модель и предлагает выбор результатов для получения.

Открыть новый Reader модель, которую программное обеспечение создало в <current_folder>\sldv_output\Reader

Новый блок A Inport записывает данные в хранилище данных, которое используется подсистемой Reader в новой модели.

Подсистема вызова функций - это запускаемая подсистема, выполнение которой определяется логикой, внутренней для S-функции C MEX, а не значением сигнала. Подсистемы функционального вызова всегда являются атомарными.

Примечание

Дополнительные сведения см. в разделе Реализация функциональных подсистем вызовов с S-функциями.

При анализе модели с помощью подсистемы вызова функций Simulink Design Verifier создает новую модель с блоком Inport, имитирующим триггер и копию подсистемы. Затем программа анализирует новую модель.

В следующем примере анализируется подсистема вызова функции в sl_subsys_fcncall2 модель:

Откройте окно sl_subsys_fcncall2 пример модели:

Эта модель содержит диаграмму Stateflow с именем Chart, которая запускает подсистему вызова функций f.

Щелкните правой кнопкой мыши подсистему f и выберите Design Verifier > Generate Tests for Subsystem.

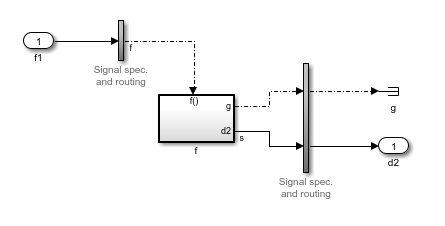

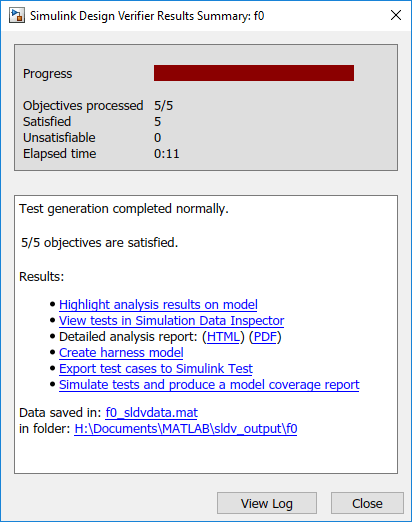

Программа извлекает подсистему в новую модель с именем f0, анализирует извлеченную модель и создает результаты.

Откройте окно f0 модель, которую программное обеспечение создало в <current_folder>\sldv_output\f0

Блок Inport и блок новой подсистемы имитируют триггер для подсистемы функционального вызова f в новом f0 модель.