Вычисляет скорость преобразования Фурье (FFT) для стандартной полосы пропускания передачи LTE 15 МГц

Беспроводная панель инструментов HDL/модуляция

Блок FFT 1536 предназначен для поддержки стандартной полосы пропускания LTE 15 МГц. Этот блок используется в работе блока демодулятора OFDM LTE. Блок принимает входные данные вместе с действительным управляющим сигналом и выводит потоковые данные с samplecontrol автобус.

Блок обеспечивает архитектуру, подходящую для генерации кода HDL и аппаратного развертывания.

data - Входные данныеВходные данные, заданные как скаляр вещественных или комплексных значений.

double и single типы данных поддерживаются для моделирования, но не для генерации кода HDL.

Чем больше дробных битов в длине входного слова, тем лучше точность при выводе.

Типы данных: double | single | int8 | int16 | int32 | fixed point

Поддержка комплексного номера: Да

valid - Указывает допустимые входные данныеУказывает, являются ли входные данные допустимыми. При допустимом вводе: 1 (true), блок фиксирует значение на входном порте данных. При допустимом вводе: 0 (false), блок игнорирует выборки входных данных.

Типы данных: Boolean

reset - Сигнал управления сбросомКогда это значение равно 1 (true), блок останавливает текущий расчет и очищает все внутренние состояния.

Чтобы включить этот порт, выберите параметр Enable reset input port.

Типы данных: Boolean

data - Выходные данные частотного каналаВыходные данные частотного канала, возвращаемые в виде скаляра вещественных или комплексных значений.

Когда вход имеет значение fixed point тип данных, тип выходных данных совпадает с типом входных данных. Если вход имеет целочисленный тип, то выходной тип данных имеет значение fixed point тип.

Типы данных: double | single | int8 | int16 | int32 | fixed point

Поддержка комплексного номера: Да

ctrl - Управляющие сигналы, сопровождающие поток пробsamplecontrol автобусУправляющие сигналы, сопровождающие поток проб, возвращаемые в виде samplecontrol Шина включает в себя start, end, и valid управляющие сигналы, которые указывают границы кадра и достоверность выборок.

start - Указывает начало выходного кадра.

end - Указывает конец выходного кадра

valid - Указывает, что данные порта выходных данных являются допустимыми

Дополнительные сведения см. в разделе Пример шины управления.

Типы данных: bus

Complex multiplication - внедрение ЛПВПUse 3 multipliers and 5 adders (по умолчанию) | Use 4 multipliers and 2 addersОпределяет тип комплексного множителя для реализации HDL. Каждое умножение реализуется либо с Use 3 multipliers and 5 adders или с Use 4 multipliers and 2 adders. Скорость реализации зависит от используемого средства синтеза и целевого устройства.

Rounding method - Режим округления для внутренних расчетов с фиксированной точкойFloor (по умолчанию) | Ceiling | Convergent | Nearest | Round | ZeroУказывает тип метода округления для внутренних вычислений с фиксированной точкой. Дополнительные сведения о методах округления см. в разделе Режимы округления (панель инструментов системы DSP). Если входным значением является целое число или тип данных с фиксированной точкой, этот блок использует арифметику с фиксированной точкой для внутренних вычислений. Этот параметр не применяется, когда входные данные single или double.

Normalize butterfly output - Нормализация выходных данныхoff (по умолчанию) | onПри выборе этого параметра блок делит выходные данные на 1536. Эта опция полезна, если требуется, чтобы выходной сигнал блока оставался в том же диапазоне амплитуд, что и его входной сигнал. Эта опция требуется при вводе значения fixed point тип.

При выборе этого параметра длина выходного слова увеличивается на 2 бита, а при сбросе этого параметра длина выходного слова увеличивается на 11 битов.

Enable reset input port - Дополнительный сигнал сбросаoff (по умолчанию) | onВыберите этот параметр для активизации порта сброса.

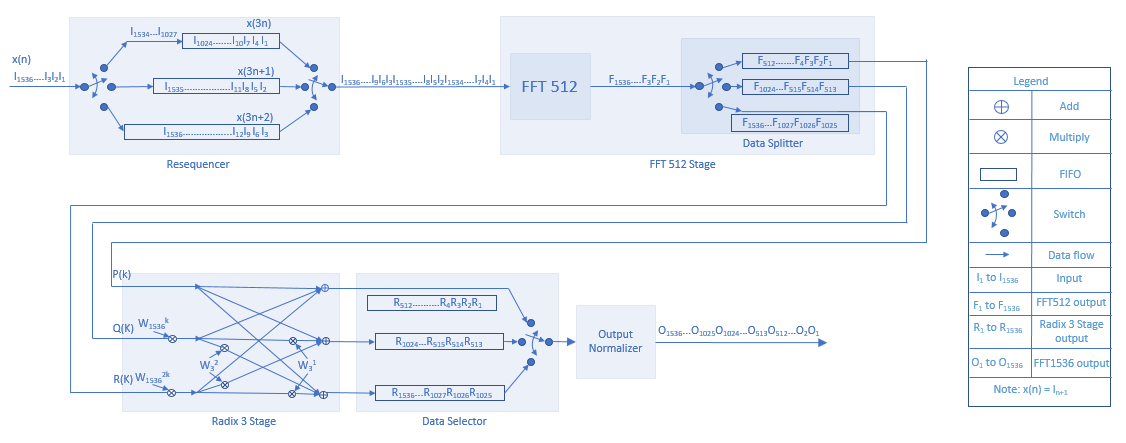

Для проектирования блока FFT 1536 реализован алгоритм прореживания по радиусу-3 (DIT). Входная последовательность x (n) для всех n = {0,1,2.... 1535} делится на три последовательности DIT, x (3n), x (3n + 1), x (3n + 2) для всех n = {0,1,2.... 511}.

Это уравнение определяет вычисление БПФ 1536 данной последовательности x (n).

.., 1535

Уравнение может быть реализовано делением его на три части, где P (k), Q (k), R (k) - N/3 (FFT 512) точка FFT x (3n), x (3n + 1) и x (3n + 2) соответственно. Здесь N = 1536, а k = 0,1,2,....., 511.

WN2kR (k)

W32WN2kR (k)

W31WN2kR (k)

Эта диаграмма показывает внутреннюю архитектуру блока и то, как входная последовательность проходит через компоненты блока.

Входная последовательность x (n) демультиплексирована на три последовательности DIT, x (3n), x (3n + 1), x (3n + 2), каждая длиной 512. Три запоминающих устройства FIFO хранят эти последовательности. Эти DIT-последовательности сериализуются и передаются потоком через блок FFT 512.

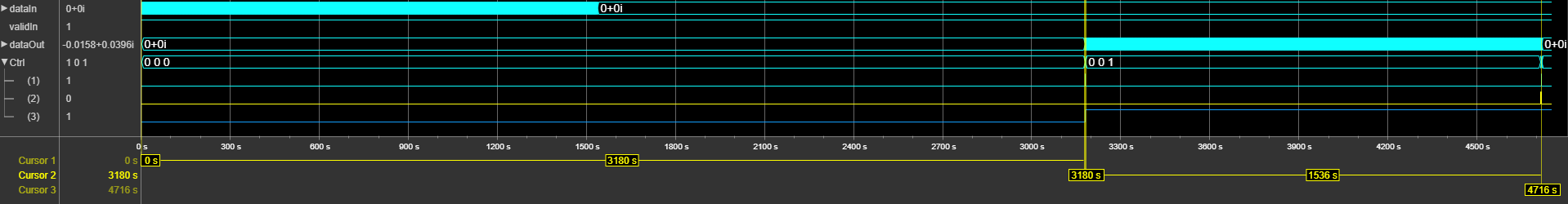

На этом рисунке показана форма выходного сигнала блока при работе с параметрами конфигурации по умолчанию. Блок выдает выходные данные после задержки 3180 тактовых циклов. Длина выходных данных между start (Ctrl. (1)) иend (Ctrl. (2)) выходные управляющие сигналы составляют 1536 тактовых циклов.

Производительность синтезированного HDL-кода зависит от цели и вариантов синтеза. В этой таблице представлены результаты синтеза данных о ресурсах и рабочих характеристиках блока с параметрами конфигурации по умолчанию, с включенной функцией нормализации и с входными данными в fixdt(1,17,15) формат. Сгенерированный HDL предназначен для платы Xilinx ® Zynq ® XC7Z045-FFG900-2 FPGA. В конструкции достигается тактовая частота 355 МГц.

| Ресурс | Используемый номер |

|---|---|

| LUTs | 7330 |

| Регистры | 9325 |

| Блокировать RAM | 18 |

| DSPs | 36 |

Этот блок поддерживает генерацию кода C/C + + для режимов ускорения Simulink ® и быстрого ускорения, а также для генерации компонентов DPI.

HDL Coder™ предоставляет дополнительные опции конфигурации, которые влияют на реализацию HDL и синтезированную логику.

Этот блок имеет единую архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках проекта. Распределенная конвейерная обработка не перераспределяет эти регистры. Значение по умолчанию: |

| InputPipeline | Количество входных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

| OutputPipeline | Количество выходных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: |

Невозможно создать HDL для этого блока в переустановляемой синхронной подсистеме (кодере HDL).

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.