Примечание

Этот раздел ссылается на сгенерированный VHDL® сущности или Verilog® модули в общем виде как «сущности».

mapping file - это текстовый файл отчета, сгенерированный makehdl. Файлы отображения генерируются как средство отслеживания сгенерированных HDL сущностей обратно в соответствующие системы модели.

Файл отображения показывает отношения между системами в модели и сущностями VHDL или модулями Verilog, которые были сгенерированы из них. Запись файла отображения имеет форму

path --> HDL_name

path - полный путь к системе в модели и HDL_name - имя сущности VHDL или модуля Verilog, сгенерированного из этой системы. Файл отображения содержит по одной записи на линию.В простых случаях файл отображения может содержать только одну запись. Для примера, symmetric_fir подсистема sfir_fixed модель генерирует следующий файл отображения:

sfir_fixed/symmetric_fir --> symmetric_fir

Файлы отображения более полезны, когда HDL-код генерируется из сложных моделей, где несколько подсистем генерируют много сущностей, и в случаях, когда конфликты между идентично именованными подсистемами разрешаются HDL- Coder™.

Если имя подсистемы уникально в модели, HDL Coder просто использует имя подсистемы как имя сгенерированной сущности. Там, где встречаются одинаково именованные подсистемы, кодер пытается разрешить конфликт, добавляя постфиксную строку (по умолчанию '_entity') к конфликтующей подсистеме. Если впоследствии сгенерированные имена сущностей конфликтуют в свою очередь с этим именем, добавочные числа (1,2,3,... ) прилагаются.n

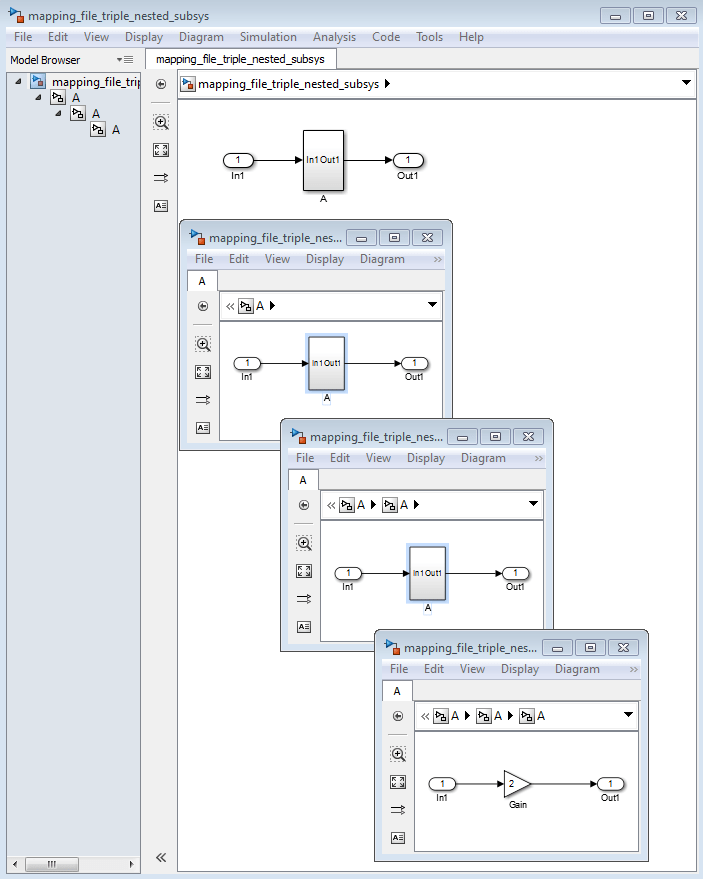

В качестве примера рассмотрим модель, показанную на следующем рисунке. Модель верхнего уровня содержит подсистемы с именем A вложенный в три уровня.

Когда код генерируется для подсистемы верхнего уровня A, makehdl работает с самого глубокого уровня иерархии модели, генерируя уникальные имена сущностей для каждой подсистемы.

makehdl('mapping_file_triple_nested_subsys/A')

### Working on mapping_file_triple_nested_subsys/A/A/A as A_entity1.vhd

### Working on mapping_file_triple_nested_subsys/A/A as A_entity2.vhd

### Working on mapping_file_triple_nested_subsys/A as A.vhd

### HDL Code Generation Complete.

В следующем примере приводится содержимое результирующего файла отображения.

mapping_file_triple_nested_subsys/A/A/A --> A_entity1 mapping_file_triple_nested_subsys/A/A --> A_entity2 mapping_file_triple_nested_subsys/A --> A

Учитывая эту информацию, можно проследить сгенерированную сущность назад в ее соответствующую подсистему при помощи open_system команда, для примера:

open_system('mapping_file_triple_nested_subsys/A/A')

Каждый сгенерированный файл сущности также содержит путь к соответствующей подсистеме в комментариях заголовка в верхней части файла, как в следующем фрагменте кода.

-- Module: A_entity2 -- Simulink Path: mapping_file_triple_nested_subsys/A -- Hierarchy Level: 0