Распределённая конвейеризация, или рециркуляция регистров, является оптимизацией скорости, которая перемещает существующие задержки в проекте, чтобы уменьшить критический путь с сохранением функционального поведения.

Программное обеспечение HDL Coder™ использует адаптацию алгоритма ретиминга Лейзерсона-Саксен.

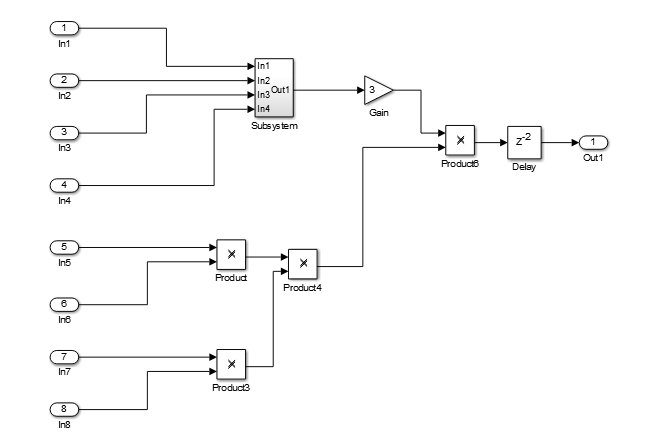

Для примера в следующей модели существует задержка 2 на выходе.

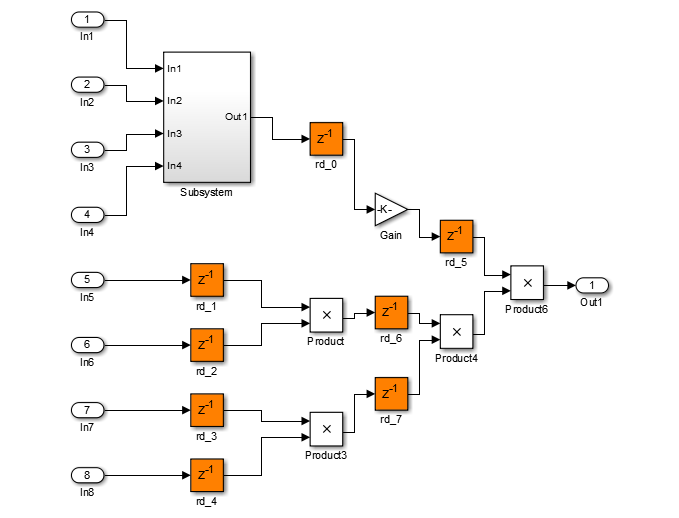

Следующая схема показывает сгенерированную модель после того, как распределённая конвейеризация перераспределяет задержку, чтобы уменьшить критический путь.

Распределённая конвейеризация может уменьшить критический путь вашего проекта, что позволит вам использовать более высокую тактовую частоту и увеличить пропускную способность.

Однако распределённая конвейеризация требует, чтобы ваш проект содержал ряд задержек. Если вам нужно вставить дополнительные задержки в проект, чтобы включить распределённую конвейеризацию, это увеличивает площадь и начальную задержку проекта.

Распределённая конвейеризация требует, чтобы ваш проект содержал задержки или регистры, которые могут быть перераспределены. Для вставки дополнительных регистров можно использовать конвейерную конвейеризацию входных данных или конвейерную конвейеризацию выходных данных.

Если ваш проект сначала не соответствует вашим требованиям к времени, попробуйте добавить больше задержек или регистров, чтобы улучшить ваши результаты.

Можно задать распределённую конвейеризацию для подсистемы и Stateflow® графики и MATLAB Function блоки в подсистеме. Смотрите раздел «Вставка распределенного трубопровода» для блоков MATLAB function.

Чтобы задать распределённую конвейеризацию с помощью пользовательского интерфейса:

На вкладке Apps выберите HDL Coder. Появится вкладка HDL Code. Выберите Subsystem и нажмите HDL Block Properties. Установите для DistributedPipelining значение on и нажмите OK.

Щелкните правой кнопкой мыши по Subsystem и выберите HDL Code > HDL Block Properties. Установите для DistributedPipelining значение on и нажмите OK.

Чтобы включить распределённую конвейеризацию, в командной строке введите:

hdlset_param('path/to/block', 'DistributedPipelining', 'on')

Совет

Выходные данные могут быть в недопустимом состоянии первоначально, если вы вставляете регистры конвейера. Чтобы избежать ошибок испытательного стенда, возникающих из-за начальных недопустимых выборок, отключите проверку выхода для этих выборок. Для получения дополнительной информации смотрите Игнорировать проверку выходных данных (количество выборок).

Оптимизация распределённой конвейеризации имеет следующие ограничения:

Результаты конвейеризации могут не быть оптимальными в оборудовании, потому что задержки оператора в целевом компьютере могут отличаться от предполагаемых задержек оператора, используемых алгоритмом распределенной конвейеризации.

Программное обеспечение HDL Coder генерирует регистры конвейера на выходах в следующих ситуациях вместо распределения регистров, чтобы уменьшить критический путь:

Диаграмма Stateflow, содержащая состояние, локальную переменную или матрицу со статически неразрешимым индексом.

HDL Coder распределяет конвейерные регистры вокруг следующих блоков, а не внутри них:

Model

Sum (Cascade реализация)

Product (Cascade реализация)

MinMax

Upsample

Downsample

Rate Transition

Zero-Order Hold

Reciprocal Sqrt (RecipSqrtNewton реализация)

Trigonometric Function (CORDIC Приближение)

Single Port RAM

Dual Port RAM

Simple Dual Port RAM

Если вы включите распределенную конвейеризацию для подсистемы, которая содержит эти блоки, HDL Coder генерирует сообщение во время генерации кода. Чтобы исправить это сообщение, поместите эти блоки в одну или несколько подсистем в исходной подсистеме и отключите иерархическую распределенную конвейеризацию. HDL Coder распределяет регистры конвейера вокруг вложенных подсистем.

M-PSK Demodulator Baseband

M-PSK Modulator Baseband

QPSK Demodulator Baseband

QPSK Modulator Baseband

BPSK Demodulator Baseband

BPSK Modulator Baseband

PN Sequence Generator

Repeat

HDL Counter

LMS Filter

Sine Wave

Viterbi Decoder

Triggered Subsystem

Counter Limited

Counter Free-Running

Frame Conversion

Чтобы увидеть информацию о распределённой конвейеризации в отчете, прежде чем вы сгенерируете код для каждой подсистемы или модели-ссылки, включите отчет оптимизации. Чтобы включить этот отчет, на вкладке HDL Code, выберите Report Options, а затем Generate optimization report.

Когда вы генерируете отчет оптимизации, в разделе Distributed Pipelining, вы видите эффект распределенной оптимизации конвейеризации. Если распределенная конвейеризация не удалась, в отчете показываются диагностические сообщения и блоки, из-за чего распределенная конвейеризация не удалась.

Если распределённая конвейеризация успешна, в отчете отображаются сравнительные списки регистров до и после применения преобразования распределённой конвейеризации.

Лейсерсон, К. Э. и Джеймс Б. Саксен. «Синхронизация синхронной схемы». Алгоритмика. Том 6, № 1, 1991, стр. 5-35.