Чтобы изменить XML- файл определения платы, сначала сделайте его доступным для записи. Если файл доступен только для чтения, редактор плат FPGA позволяет просматривать только информацию о строении платы. Вы не можете изменять эту информацию.

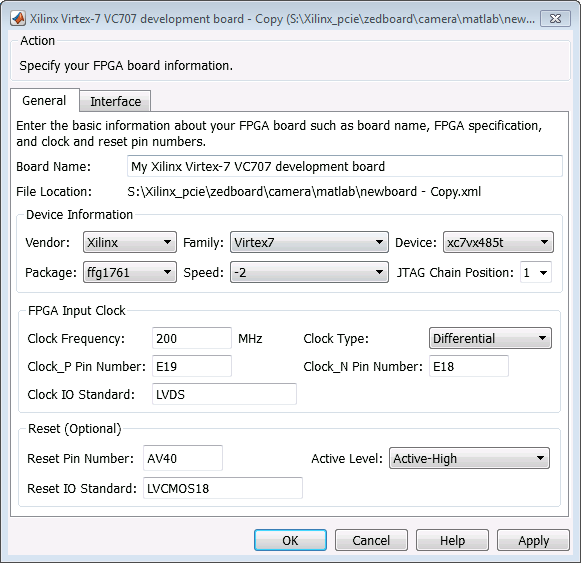

Board Name: Уникальное имя платы

Device Information:

Vendor: Xilinx или Altera

Family: Семейство зависит от указанного поставщика. Соответствующие настройки см. в файле спецификаций плат.

Device: Устройство зависит от указанного поставщика и семейства. Соответствующие настройки см. в файле спецификаций плат.

Для Xilinx® только платы:

Package: Пакет зависит от указанного поставщика, семейства и устройства. Соответствующие настройки см. в файле спецификаций плат.

Speed: Скорость зависит от пакета. Соответствующие настройки см. в файле спецификаций плат.

JTAG Chain Position: Значение указывает начальное положение для цепи JTAG. Для получения этой информации см. файл спецификаций плат.

FPGA Input Clock. Подробные данные о часах требуются для рабочих процессов FIL и «под ключ». Всю необходимую информацию можно найти в файле спецификаций платы.

Clock Frequency. Должно быть от 5 до 300. Для интерфейса Ethernet предлагаемые тактовые частоты составляют 50, 100, 125 и 200 МГц.

Clock Type: Single_Ended или Differential.

Clock Pin Number (Single_Ended) - Необходимо указать. Пример: N10.

Clock_P Pin Number (дифференциальный) - должен быть задан. Пример: E19.

Clock_N Pin Number (дифференциальный) - должен быть задан. Пример: E18.

Clock IO Standard - программируемый стандарт ввода-вывода для конфигурирования входных, выходных или двунаправленных портов. Для примера, LVDS.

Reset (Optional). Если необходимо указать сброс, найдите номер контакта и активный уровень в файле спецификаций платы и введите эту информацию.

Reset Pin Number. Оставьте пустым, если у вас его нет.

Active Level : Active-Low или Active-High.

Reset IO Standard - программируемый стандарт ввода-вывода для конфигурирования входных, выходных или двунаправленных портов. Для примера, LVCMOS33.

На странице Interface описываются поддерживаемые интерфейсы ввода-вывода FPGA. Выберите любой из перечисленных интерфейсов и щелкните View, чтобы увидеть Signal List. Если файл определения платы имеет разрешение на запись, можно также Add New интерфейс, Edit интерфейс или Remove интерфейс.

Примечание

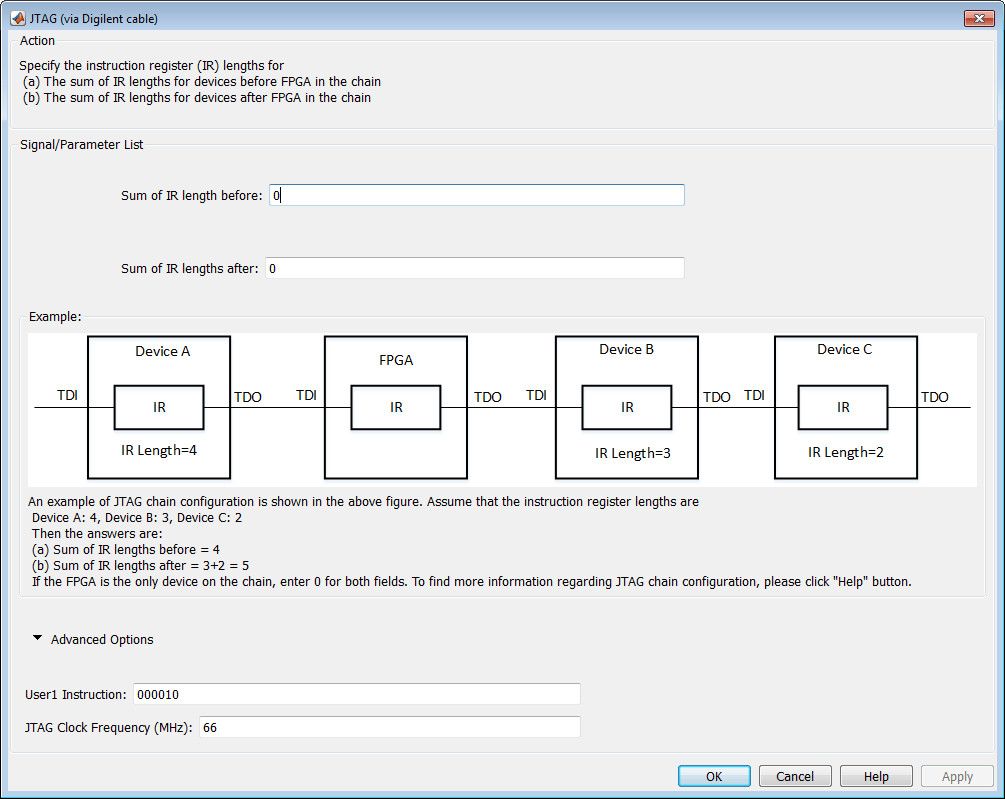

Тщательно введите информацию для настройки кабеля JTAG. Если настройки неправильны, ошибки симуляции выходят и не работают. Если вы все еще не уверены, как настроить кабель JTAG после чтения этих инструкций, обратитесь в MathWorks® техническая поддержка с подробной информацией о вашей плате.

Signal/Parameter List - Предоставить сумму длин регистров команд (IR) для всех устройств до и после FPGA в цепи.

Если FPGA является единственным элементом в цепи устройств, используйте нули как в Sum of IR length before, так и в Sum of IR length after.

Если вы используете Zynq® устройство, и это единственный элемент в цепи устройств, введите 4 в Sum of IR length before и 0 в Sum of IR length after.

Если ваша плата не соответствует любому из этих условий, следуйте этим инструкциям, чтобы получить длину ИК-сигнала:

Подключите плату FPGA к компьютеру с помощью кабеля JTAG. Включите плату.

Убедитесь, что вы установили драйверы кабеля во время Vivado® монтаж.

Откройте Vivado Hardware Manager и выберите Open a new hardware target. В диалоговом окне представлены сводные данные длин ИК-излучения для всех устройств этого целевого устройства.

Суммируйте IR-длины перед FPGA и введите общее значение в Sum of IR length before. Суммируйте IR-длины после FPGA и введите общее значение в Sum of IR length after.

Vivado Hardware Manager не может распознать длину ИК-сигнала менее распространенных устройств. Для этих устройств обратитесь к руководству по устройству для получения информации о длине регистра команд.

Advanced Options - Если значения по умолчанию не совпадают с наиболее распространенными настройками для многих устройств, установите параметры User1 Instruction и JTAG Clock Frequency (MHz). Наиболее распространенные настройки 000010 и 66, соответственно.

User1 Instruction - Инструкция USER1 JTAG, заданная в примитиве Xilinx Bscane2. Этот двоичный номер команды, заданный Xilinx, варьируется от устройства к устройству. Для большинства устройств 7-й серии эта инструкция 000010. Если ваше устройство имеет другое значение, введите его в этот параметр.

Чтобы найти это значение, посмотрите на bsd файл для вашего конкретного устройства, найденный в установке Vivado. Для примера, для XA7A32T-CPG236 устройства, bsd файл расположен в Vivado\2014.2\data\parts\xilinx\artix7\aartix7\xa7a35t\cpg236.

Откройте этот файл. The USER1 значение 000010. Введите это значение в User1 Instruction.

"USER1 (000010),"

JTAG Clock Frequency (MHz) - тактовая частота, используемая схемой JTAG. Это значение изменяется в зависимости от устройства. Вы можете найти это значение в том же bsd файл, описанный в разделе User1 Instruction. Для примера тактовая частота JTAG составляет 66 МГц для XA7A32T-CPG236 устройства:

attribute TAP_SCAN_CLOCK of TCK : signal is (66.0e6, BOTH);