HDL Coder™ могут обнаруживать атомарные подсистемы, которые идентичны или идентичны, за исключением их значений маскирующих параметров, на любом уровне иерархии модели и генерировать один переиспользуемый HDL module или entity. Переиспользуемый HDL-код генерируется как один файл и создается несколько раз.

Чтобы сгенерировать повторно используемый HDL-код для атомарных подсистем:

The DefaultParameterBehavior Simulink® Параметр конфигурации должен быть Inlined. Можно задать этот параметр в командной строке при помощи set_param или hdlsetup функция. Чтобы задать эту настройку в диалоговом окне Параметров конфигурации, вы должны иметь Simulink Coder™.

Примечание

Используя hdlsetup устанавливает InlineParams свойство к on. Включение этого параметра аналогично установке DefaultParameterBehavior на Inlined. Настройка InlineParams на off изменяет DefaultParameterBehavior значение в Tunable.

Функции логгирования не должны использоваться, такие как логгирования сигналов или использование блоков, таких как To Workspace или To File.

Атомарные подсистемы должны быть идентичными или идентичными, за исключением их маскировочных значений параметров.

MaskParameterAsGeneric должен быть on. Для получения дополнительной информации смотрите Сгенерировать параметризованный HDL-код из маскированной подсистемы.

Параметры маски должны быть нетронутыми. Генератор кода не разделяет атомарные подсистемы с параметрами маски, которые настраиваются.

Типы данных параметров маски не могут быть double или single.

Настраиваемый параметр должен использоваться только в Constant или Gain блоках.

Типы данных портов должны совпадать.

Если вы измените значение настраиваемого параметра маски, может измениться тип данных порта выхода. Если одна из атомарных подсистем имеет другой тип данных портов, код, сгенерированный для этой подсистемы, также отличается.

Чтобы сгенерировать повторно используемый HDL-код для виртуальных подсистем:

The DefaultParameterBehavior Параметр конфигурации Simulink должен быть Inlined. Можно задать этот параметр в командной строке при помощи set_param или hdlsetup функция. Чтобы задать эту настройку в диалоговом окне Параметров конфигурации, у вас должен быть Simulink Coder.

Примечание

Используя hdlsetup устанавливает InlineParams свойство к on. Включение этого параметра аналогично установке DefaultParameterBehavior на Inlined. Настройка InlineParams на off изменяет DefaultParameterBehavior значение в Tunable.

Функции логгирования не должны использоваться, такие как логгирования сигналов или использование блоков, таких как To Workspace или To File.

Виртуальные подсистемы должны быть идентичными или идентичными, за исключением их маскировочных значений параметров.

SubsystemReuse должно быть установлено в 'Atomic and Virtual'.

Настройка SubsystemReuse на 'Atomic and Virtual' уменьшает искусственные алгебраические ошибки и улучшает распознавание идентичных подсистем, независимо от их топологии в остальной части проекта. Идентификация аналогичных подсистем может помочь совместному использованию ресурсов.

Чтобы установить эти значения в требуемую настройку, в Командном Окне MATLAB, введите:

hdlset_param('myHDLModel', 'SubsystemReuse', 'Atomic and Virtual')

Также можно задать эту опцию на панели HDL Code Generation верхнего уровня в диалоговом окне Параметры конфигурации (Configuration Parameters). В разделе Global Settings > Coding style можно изменить настройку Code reuse на необходимую опцию.

Предыдущие команды устанавливают SubsystemReuse опция для вашего проекта. Чтобы задать эту опцию только для текущего сеанса генерации кода, введите:

makehdl(<DUT system>, 'SubsystemReuse', 'Atomic and Virtual')

MaskParameterAsGeneric должен быть on. Для получения дополнительной информации смотрите Сгенерировать параметризованный HDL-код из маскированной подсистемы.

Параметры маски должны быть нетронутыми. Генератор кода не разделяет атомарные подсистемы с параметрами маски, которые настраиваются.

Типы данных параметров маски не могут быть double или single.

Настраиваемый параметр должен использоваться только в Constant или Gain блоках.

Типы данных портов должны совпадать.

Если вы измените значение настраиваемого параметра маски, может измениться тип данных порта выхода. Если одна из атомарных подсистем имеет другой тип данных портов, код, сгенерированный для этой подсистемы, также отличается.

Если ваш проект содержит идентичные атомарные подсистемы, кодер генерирует один HDL module или entity для подсистемы и создает ее несколько экземпляров.

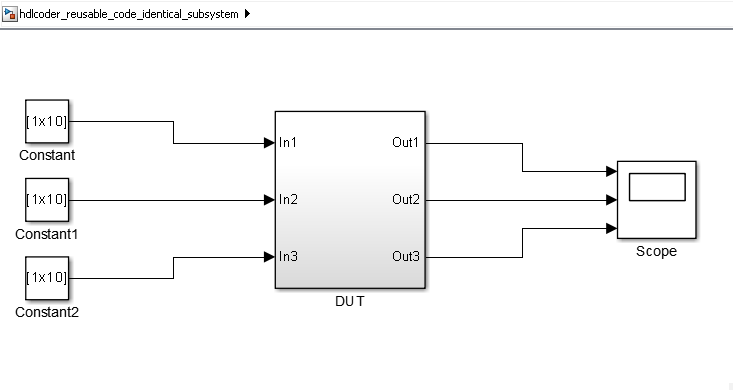

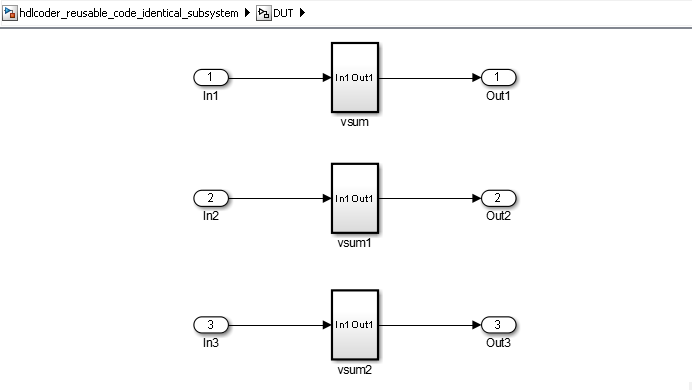

The hdlcoder_reusable_code_identical_subsystem модель показывает пример подсистемы DUT, содержащей три идентичные атомарные подсистемы.

HDL Coder генерирует один VHDL® файл, vsum.vhd, для трех подсистем.

makehdl('hdlcoder_reusable_code_identical_subsystem/DUT')### Generating HDL for 'hdlcoder_reusable_code_identical_subsystem/DUT'.

### Starting HDL check.

### Generating new validation model: gm_hdlcoder_reusable_code_identical_subsystem_vnl.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoder_reusable_code_identical_subsystem'.

### Working on hdlcoder_reusable_code_identical_subsystem/DUT/vsum/Sum of Elements as

hdl_prj\hdlsrc\hdlcoder_reusable_code_identical_subsystem\Sum_of_Elements.vhd.

### Working on hdlcoder_reusable_code_identical_subsystem/DUT/vsum as

hdl_prj\hdlsrc\hdlcoder_reusable_code_identical_subsystem\vsum.vhd.

### Working on hdlcoder_reusable_code_identical_subsystem/DUT as

hdl_prj\hdlsrc\hdlcoder_reusable_code_identical_subsystem\DUT.vhd.

### Generating package file hdl_prj\hdlsrc\hdlcoder_reusable_code_identical_subsystem\DUT_pkg.vhd.

### Creating HDL Code Generation Check Report DUT_report.html

### HDL check for 'hdlcoder_reusable_code_identical_subsystem' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.Сгенерированный код для подсистемы DUT, DUT.vhd, содержит три экземпляра vsum компонент.

ARCHITECTURE rtl OF DUT IS

-- Component Declarations

COMPONENT vsum

PORT( In1 : IN vector_of_std_logic_vector16(0 TO 9); -- int16 [10]

Out1 : OUT std_logic_vector(19 DOWNTO 0) -- sfix20

);

END COMPONENT;

-- Component Configuration Statements

FOR ALL : vsum

USE ENTITY work.vsum(rtl);

-- Signals

SIGNAL vsum_out1 : std_logic_vector(19 DOWNTO 0); -- ufix20

SIGNAL vsum1_out1 : std_logic_vector(19 DOWNTO 0); -- ufix20

SIGNAL vsum2_out1 : std_logic_vector(19 DOWNTO 0); -- ufix20

BEGIN

u_vsum : vsum

PORT MAP( In1 => In1, -- int16 [10]

Out1 => vsum_out1 -- sfix20

);

u_vsum1 : vsum

PORT MAP( In1 => In2, -- int16 [10]

Out1 => vsum1_out1 -- sfix20

);

u_vsum2 : vsum

PORT MAP( In1 => In3, -- int16 [10]

Out1 => vsum2_out1 -- sfix20

);

Out1 <= vsum_out1;

Out2 <= vsum1_out1;

Out3 <= vsum2_out1;

END rtl;Если ваш проект содержит атомарные подсистемы, которые идентичны, за исключением их настраиваемых значений параметров маски, можно сгенерировать один HDL module или entity для подсистемы. В сгенерированном коде module или entity создается несколько экземпляров.

Чтобы сгенерировать повторно используемый код для идентичных атомарных подсистем, включите MaskParameterAsGeneric для модели. По умолчанию MaskParameterAsGeneric отключен.

Для примера включить генерацию переиспользуемого кода для атомарных подсистем с настраиваемыми параметрами в hdlcoder_reusable_code_parameterized_subsystem модель, введите:

hdlset_param('hdlcoder_reusable_code_parameterized_subsystem','MaskParameterAsGeneric','on')

Кроме того, в диалоговом окне Параметров конфигурации, на вкладке HDL Code Generation > Global Settings > Coding Style, включите опцию Generate parameterized HDL code from masked subsystem.

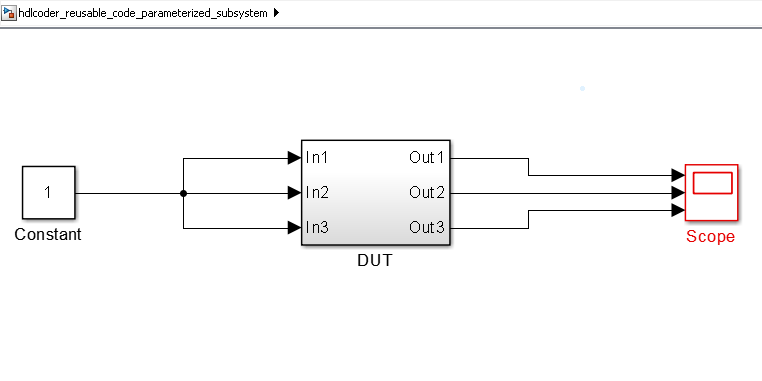

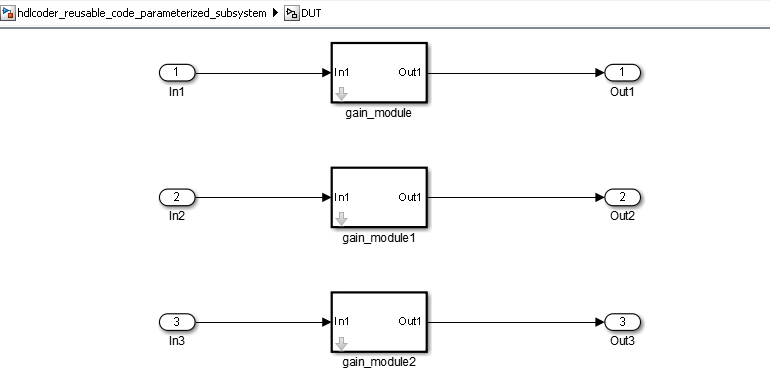

The hdlcoder_reusable_code_parameterized_subsystem модель показывает пример подсистемы DUT, содержащей атомарные подсистемы, которые идентичны, за исключением их настраиваемых значений параметров маски.

В hdlcoder_reusable_code_parameterized_subsystem/DUTмодули усиления являются подсистемами со значениями усиления, представленными параметрами настраиваемой маски. Значения усиления: 4 для gain_module, 5 для gain_module1, и 7 для gain_module2.

С MaskParameterAsGeneric включено, HDL Coder генерирует один исходный файл, gain_module.v, для трех подсистем модуля усиления.

makehdl('hdlcoder_reusable_code_parameterized_subsystem/DUT','MaskParameterAsGeneric','on',... 'TargetLanguage','Verilog')

### Generating HDL for 'hdlcoder_reusable_code_parameterized_subsystem/DUT'.

### Starting HDL check.

### Begin Verilog Code Generation for 'hdlcoder_reusable_code_parameterized_subsystem'.

### Working on hdlcoder_reusable_code_parameterized_subsystem/DUT/gain_module as

hdlsrc\hdlcoder_reusable_code_parameterized_subsystem\gain_module.v.

### Working on hdlcoder_reusable_code_parameterized_subsystem/DUT as

hdlsrc\hdlcoder_reusable_code_parameterized_subsystem\DUT.v.

### Creating HDL Code Generation Check Report DUT_report.html

### HDL check for 'hdlcoder_reusable_code_parameterized_subsystem' complete with 0 errors, 0 warnings, and 0 messages.

### HDL code generation complete.Сгенерированный код для подсистемы DUT, DUT.v, содержит три экземпляра gain_module компонент.

module DUT

(

In1,

In2,

In3,

Out1,

Out2,

Out3

);

input [7:0] In1; // uint8

input [7:0] In2; // uint8

input [7:0] In3; // uint8

output [31:0] Out1; // uint32

output [31:0] Out2; // uint32

output [31:0] Out3; // uint32

wire [31:0] gain_module_out1; // uint32

wire [31:0] gain_module1_out1; // uint32

wire [31:0] gain_module2_out1; // uint32

gain_module # (.myGain(4)

)

u_gain_module (.In1(In1), // uint8

.Out1(gain_module_out1) // uint32

);

assign Out1 = gain_module_out1;

gain_module # (.myGain(5)

)

u_gain_module1 (.In1(In2), // uint8

.Out1(gain_module1_out1) // uint32

);

assign Out2 = gain_module1_out1;

gain_module # (.myGain(7)

)

u_gain_module2 (.In1(In3), // uint8

.Out1(gain_module2_out1) // uint32

);

assign Out3 = gain_module2_out1;

endmodule // DUTВ gain_module.v, а myGain Verilog®

parameter генерируется для настраиваемого параметра маски.

module gain_module

(

In1,

Out1

);

input [7:0] In1; // uint8

output [31:0] Out1; // uint32

parameter [31:0] myGain = 4; // ufix32

wire [31:0] kconst; // ufix32

wire [39:0] Gain_mul_temp; // ufix40

wire [31:0] Gain_out1; // uint32

assign kconst = myGain;

assign Gain_mul_temp = kconst * In1;

assign Gain_out1 = Gain_mul_temp[31:0];

assign Out1 = Gain_out1;

endmodule // gain_module