В HDL Workflow Advisor можно выбрать Processor/FPGA synchronization mode для процессора и FPGA, когда вы:

Сгенерируйте пользовательское IP-ядро для использования во встроенной системе интегрирования проекта.

Используйте рабочий процесс Simulink Real-Time FPGA I/O.

Доступны следующие режимы синхронизации:

Free running (по умолчанию)

Coprocessing – blocking

Coprocessing – nonblocking with delay (доступно только для Simulink Real-Time FPGA I/O рабочего процесса)

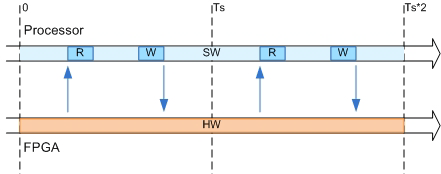

В режиме свободного запуска процессор и FPGA запускаются несовпадающими, непрерывно и параллельно.

Выберите Free running в качестве Processor/FPGA synchronization mode, когда вы не хотите, чтобы ваш процессор и FPGA были автоматически синхронизированы.

Следующая схема показывает, как процессор и FPGA могут обмениваться данными в режиме свободного запуска. Затененные области указывают, что процессор и FPGA работают постоянно.

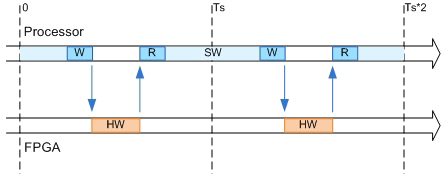

В режиме блокировки сопроцессора HDL- Coder™ автоматически генерирует логику синхронизации для FPGA так, чтобы процессор и FPGA выполнялись совместно.

Выберите Coprocessing – blocking как Processor/FPGA synchronization mode, когда время выполнения FPGA является коротким относительно шага расчета процессора, и вы хотите, чтобы FPGA завершил до продолжения работы процессора.

Следующая схема показывает, как процессор и FPGA запускаются в режиме блокировки совмещения.

Затененные области указывают, когда процессор и FPGA работают. В течение каждого шага расчета процессор записывает данные в FPGA, затем останавливается и ожидает указания, что FPGA закончил обработку, прежде чем продолжить выполнение. Каждый раз, когда FPGA запускается, он выполняет логику, сгенерированную для одного шага расчета подсистемы DUT.

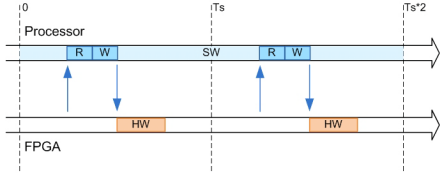

В режиме сопроцессора с задержкой без блокировки HDL Coder автоматически генерирует логику синхронизации для FPGA, так что процессор и FPGA запускаются совместно. Этот режим доступен только для модулей ввода-вывода Speedgoat, которые используют Xilinx® ISE с Simulink Real-Time FPGA I/O рабочим процессом.

Выберите Coprocessing – nonblocking with delay в качестве Processor/FPGA synchronization mode, когда время вычислений FPGA является большим относительно шага расчета процессора, или вы не хотите, чтобы процессор ждал завершения FPGA, прежде чем процессор продолжит работать.

Следующая схема показывает, как процессор и FPGA работают в режиме сопроцессора с задержкой без блокировки.

Затененные области указывают, когда процессор и FPGA работают. В течение каждого шага расчета процессор считывает данные FPGA из предыдущего шага расчета, затем записывает в FPGA и продолжает запускаться, не дожидаясь завершения FPGA. Каждый раз, когда FPGA запускается, он выполняет логику, сгенерированную для одного шага расчета подсистемы DUT.