Развертывание алгоритмических моделей на оборудовании FPGA позволяет проводить беспроводную проверку и верификацию. Однако разработка беспроводных коммуникационных систем для оборудования требует проекта компромиссов между аппаратными ресурсами и пропускной способностью. Ускорить проект и развертывание оборудования можно с помощью HDL-оптимизированных блоков, имеющих аппаратно подходящие интерфейсы и архитектуры, примеров готовых узлов, реализующих фрагменты физического слоя LTE и 5G NR, и автоматической генерации HDL-кода. Можно также использовать пакеты аппаратной поддержки, чтобы помочь с развертыванием и проверкой вашего проекта на реальном оборудовании.

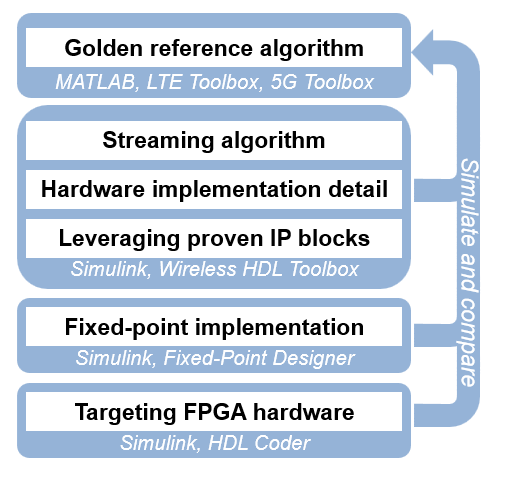

MathWorks® Продукты HDL, такие как Wireless HDL Toolbox™, позволяют начинать с математической модели, такой как MATLAB® код из LTE Toolbox™ или 5G Toolbox™, и разработайте аппаратную реализацию этого алгоритма, которая подходит для FPGA и ASIC.

Проект беспроводных коммуникаций часто начинается с разработки и тестирования алгоритмов с использованием функций MATLAB. Код MATLAB, который обычно работает с матрицами данных с плавающей точкой, хорош для разработки математических алгоритмов, манипулирования большими наборами данных и визуализации данных.

Инженеры по аппаратным средствам обычно получают математическую спецификацию от команды алгоритмов и повторно внедряют алгоритм для оборудования. Аппаратные проекты требуют компромиссов в использовании ресурсов для тактовой частоты и общей пропускной способности. Обычно этот компромисс означает работу с потоковыми данными и использование некоторой логики для управления хранением и потоком данных. Инженеры по оборудованию обычно работают на языках описания оборудования (HDL), таких как VHDL и Verilog, которые обеспечивают основанное на цикле моделирование и параллелизм.

Чтобы преодолеть эту погрешность между математическим алгоритмом и аппаратной реализацией, используйте модель алгоритма MATLAB в качестве начальной точки для аппаратной реализации. Внесите инкрементальные изменения в проект, чтобы сделать его подходящим для оборудования и продвинуться к Simulink® модель, которую вы можете использовать, чтобы автоматически сгенерировать HDL-код при помощи HDL- Coder™.

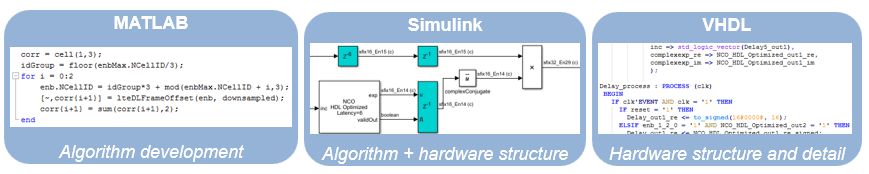

Эта схема показывает прогрессию проекта от математического алгоритма в MATLAB до аппаратно совместимой реализации в Simulink, а затем сгенерированный VHDL код.

В то время как MATLAB и Simulink поддерживают автоматическую генерацию HDL-кода, вы должны создать свой проект с учетом аппаратных требований, и Simulink лучше подходит для циклического моделирования оборудования. Он может представлять параллельные пути данных и потоковые данные с управляющими сигналами, чтобы управлять синхронизацией потока данных. Чтобы помочь в выборе типа с фиксированной точкой, он четко визуализирует распространение типа данных в проекте. Это также позволяет легко конвейерировать математические операции, чтобы улучшить максимальную тактовую частоту в оборудовании.

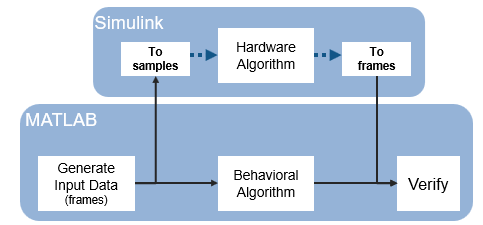

В то время как вы создаете проект, готовый к оборудованию, используйте алгоритм MATLAB в качестве «золотой ссылки», чтобы убедиться, что каждая версия проекта все еще соответствует математическим требованиям. Рабочий процесс, показанный на схеме, использует MATLAB и Simulink в качестве инструментов сотрудничества и связи между алгоритмом и оборудованием команд проектировщиков.

Например, при разработке для LTE или 5G стандартов беспроводной связи можно использовать функции LTE Toolbox и 5G Toolbox, чтобы создать золотую ссылку в MATLAB. Затем перейдите к Simulink и создайте совместимую с оборудованием реализацию с помощью библиотечных блоков из Wireless HDL Toolbox и блоков из Communications Toolbox™ и DSP System Toolbox™ которые поддержка генерацию HDL-кода. Можно повторно использовать инфраструктуру тестирования и генерации данных из MATLAB, импортировав данные из MATLAB в модель Simulink и вернув выход модели в MATLAB, чтобы проверить его по «золотой ссылке».

Библиотечные блоки из Wireless HDL Toolbox реализуют энкодеры, декодеры, модуляторы, демодуляторы и генераторы последовательности для использования в LTE, 5G или общей беспроводной коммуникационной системе. Эти блоки используют стандартный интерфейс потоковых данных для оборудования. Этот интерфейс облегчает соединение частей алгоритма вместе и включает управляющие сигналы, которые управляют потоком данных и помечают контуры системы координат. Эти блоки поддерживают автоматическую генерацию HDL-кода с HDL Coder. Можно также использовать блоки из Communications Toolbox и DSP System Toolbox, которые поддержка генерацию HDL-кода.

Блоки обеспечивают подходящую для аппаратного обеспечения архитектуры, которая оптимизирует использование ресурсов, например, включая конвейеризацию сумматора и мультипликатора, чтобы хорошо вписаться в срезы DSP FPGA. Они также поддерживают автоматические и конфигурируемые типы данных с фиксированной точкой. Использование предопределенных блоков также позволяет вам попробовать различные строения параметров, не меняя остальную часть проекта.

Для списков блоков, которые поддерживают Генерацию HDL-кода, см. Черный список Wireless HDL Toolbox (Генерация HDL-кода) (Wireless HDL Toolbox), Черный список Communications Toolbox (Генерация HDL-кода) (Communications Toolbox) и Черный список DSP System Toolbox (Генерация HDL-кода) (DSP System Toolbox).

Wireless HDL Toolbox предоставляет примеры готовых узлов, которые содержат аппаратные реализации больших частей физического слоя LTE и 5G NR. Эти проекты проверяются на соответствие «золотой ссылке» функциям, предоставляемым LTE Toolbox и 5G Toolbox. Они также были протестированы на платах FPGA, чтобы подтвердить, что они кодируют и декодируют беспроводные формы волны и используют разумное количество оборудования ресурсов. Они спроектированы таким образом, чтобы быть модульными, масштабируемыми и расширяемыми, чтобы можно было вставлять дополнительные физические каналы. Проект приемника была протестирован с помощью формы волны, захваченной вне воздуха.

Набор примеров готовых узлов включает в себя:

Генерация и 5G LTE и NR первичного и вторичного сигнала синхронизации (PSS/SSS)

Генерация и восстановление LTE нисходящего детектора общего канала управления и главного информационного блока (MIB)

Декодер первого системного информационного блока (SIB1) LTE

Аппаратно-программные модели интерфейса для MIB и SIB1 разбора битов и индексации данных оценки канала

Генерация сигналов LTE для передачи с несколькими антеннами

Поддержка FDD и TDD для LTE-передатчика и приемника

Эти примеры готовых узлов могут использоваться как есть, чтобы доставить пакетную информацию в ваше уникальное приложение и сгенерировать синтезируемые VHDL или Verilog с HDL Coder. Они также служат примерами для иллюстрации рекомендуемых практик реализации алгоритмов связи на оборудовании FPGA или ASIC.

Wireless HDL Toolbox предоставляет блоки, которые поддержка генерацию HDL-кода. Чтобы сгенерировать HDL-код из проектов, которые используют эти блоки, вы должны иметь лицензию HDL Coder. HDL Coder производит независимый от устройства код с именами сигналов, которые соответствуют модели Simulink. HDL Coder также предоставляет инструмент для управления процессом синтеза и таргетирования FPGA, и позволяет вам генерировать скрипты и испытательные стенды для использования со сторонними Симуляторами HDL.

Чтобы помочь с настройкой и нацеливанием программируемой логики на плате прототипа и проверить вашу беспроводную коммуникационную систему проекта на оборудовании, загрузите пакет аппаратной поддержки, такой как пакет поддержки Communications Toolbox для Xilinx® Zynq®- Базовое радио.