Множитель интегральной схемы

Simscape/Электрический/Интегральные схемы

Блок Multiplier моделирует множитель интегральной схемы. Блок реализует следующее уравнение, которое задает напряжение, приложенное к порту выхода:

где X1, X2, Y1, Y2, Z1, Z2 - напряжения, представленные в портах входа, A - выгода, и K коэффициент пропорциональности.

В типовой схеме умножения выход подается назад во входную Z1, что приводит к следующему усилению (принимая, что A большая):

Значение K фактора шкалы обычно изменяется внешней сетью смещения резистора. Блок Multiplier реализует K как внутренний коэффициент усиления, и внешняя сеть смещения не является необходимой для системной симуляции. Типичное значение для K - 10 с типичной регулировкой до 3.

Можно использовать блок Multiplier, чтобы реализовать ряд других функций, а также умножение. Примеры включают деление, квадраты и квадратные корни. Для получения примера схем обратитесь к таблицам данных производителя.

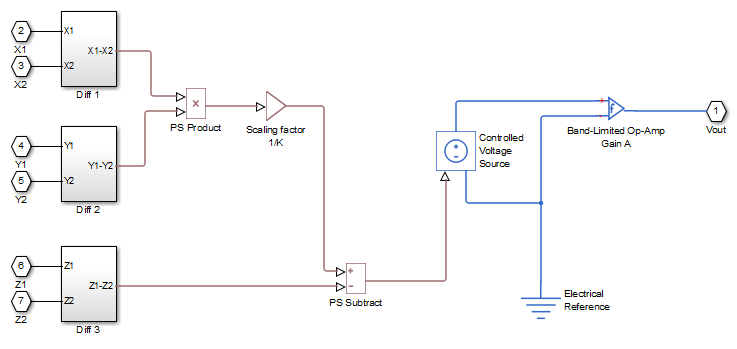

Следующий рисунок показывает структуру внутренней модели блока Multiplier. Он включает блок Band-Limited Op-Amp для моделирования конечной полосы пропускания и ограничения скорости нарастания.

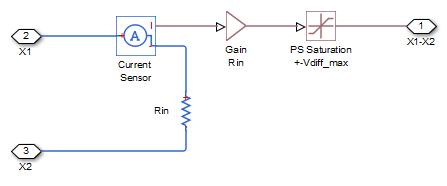

Следующий рисунок показывает один из блоков дифференциальной подсистемы. Все три блока дифференциальной подсистемы идентичны по структуре.

Реализуется только дифференциальное ограничение входов. Вы должны убедиться, что абсолютные значения используемых входов сохраняют фактическую работу устройства в его линейной области.

Выходной ток таков, что интегральная схема работает в линейной I-V области, которая может быть аппроксимирована источником напряжения плюс последовательное выходное сопротивление.

Входное напряжение смещения не моделируется, и входное отношение напряжение-ток рассматривается как линейное в области значений напряжений дифференциального сигнала.