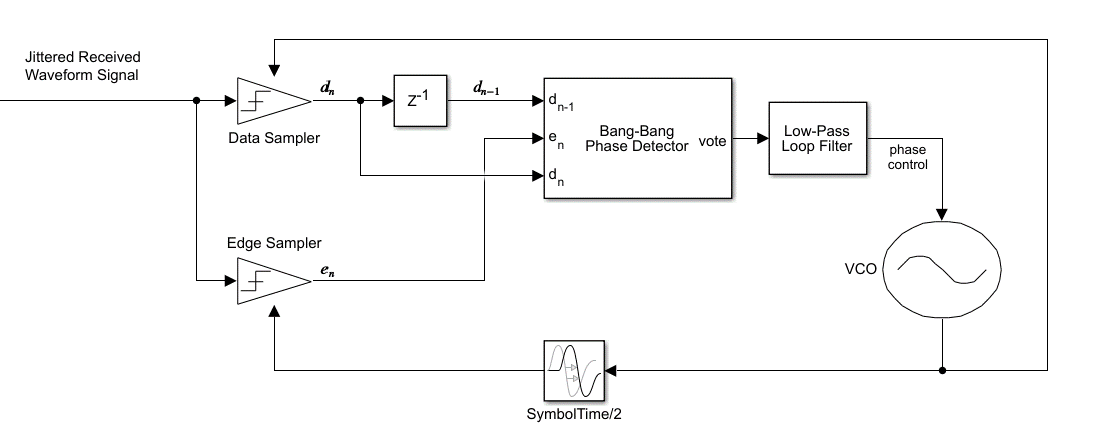

Высокоскоростные аналоговые системы SerDes используют схемы восстановления синхроимпульсов и данных (CDR), чтобы извлечь соответствующее время для правильной выборки входящей формы волны. Схема CDR создает тактовый сигнал, который выравнивается по фазе и в некоторой степени по частоте переданного сигнала. Отслеживание фазы (CDR первого порядка) обычно выполняется с помощью нелинейного релейного детектора или фазового детектора Александра, который управляет управляемым управляемым напряжением генератором (VCO). Отслеживание частоты (CDR второго порядка) интегрирует любые оставшиеся ошибки фазы и компенсирует валовые различия между синхроимпульсом ссылки передатчика и синхроимпульсом ссылки приемника. serdes.CDR и serdes.DFECDR используйте алгоритм CDR первого порядка.

Детектор фазы Alexander или bang-bang дискретизирует принятую форму волны в ребре и середине каждого символа. Краевая выборка (e n) и выборки данных (d n -1 и d n) обрабатываются с помощью некоторой цифровой логики, чтобы определить, является ли краевая выборка, и, таким образом, фаза синхроимпульса, ранней или поздней. Выборка ребра, e n и выборка данных, d n, разделяются половиной символьного времени.

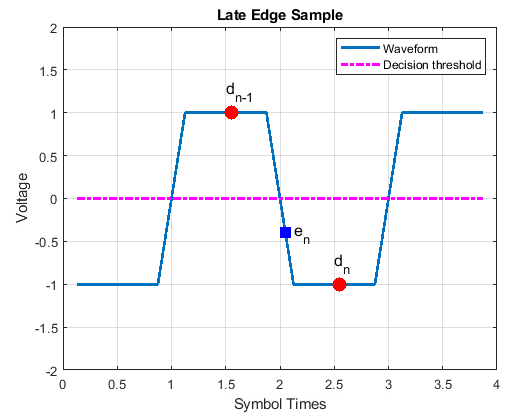

Рассмотрим форму волны, где произошел переход данных, и e n и d n ниже порогового напряжения принятия решения. Двоичные значения, разрешенные из e n и d n, совпадают, что указывает на опоздание фазы синхроимпульса.

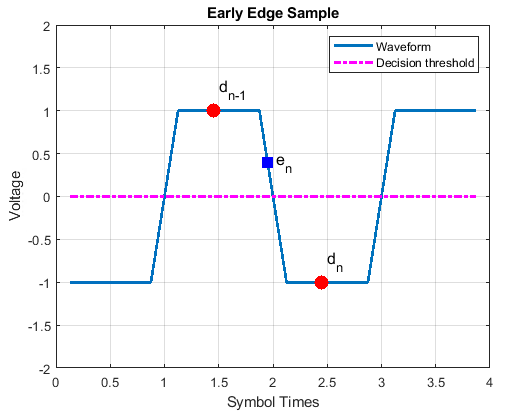

Точно так же, когда двоичные значения, разрешенные из e n и d n -1, совпадают, фаза синхроимпульса является ранней.

Представляя двоичный выход дискретизатора по ± 1, поведение фазового детектора для NRZ или PAM4 модуляции суммируется здесь:

| d n -1 | e n | d n | Действие |

|---|---|---|---|

| −1 | −1 | 1 | Фаза синхроимпульса ранняя. Сдвиньте фазу вправо. |

| 1 | 1 | −1 | |

| −1 | 1 | 1 | Фаза синхроимпульса опоздала. Сдвиньте фазу налево. |

| 1 | −1 | −1 | |

| −1 | X | −1 | Никаких действий не требуется. |

| 1 | X | 1 |

Для PAM3 модуляции уровни символов − 0,5, 0 и 0,5. Пороговые уровни по умолчанию (th) составляют ± 0,25. Таким образом, измененная таблица истинности становится:

| d n -1 | e n | d n | Действие |

|---|---|---|---|

| −0.5 | e n > − th | 0 | поздно |

| −0.5 | e n < − th | 0 | рано |

| −0.5 | e n > 0 | 0.5 | поздно |

| −0.5 | e n < 0 | 0.5 | рано |

| 0 | e n > th | 0.5 | поздно |

| 0 | e n < th | 0.5 | рано |

| 0 | e n > − th | −0.5 | рано |

| 0 | e n < − th | −0.5 | поздно |

| 0.5 | e n > th | 0 | рано |

| 0.5 | e n < th | 0 | поздно |

| 0.5 | e n > 0 | −0.5 | рано |

| 0.5 | e n < 0 | −0.5 | поздно |

Управление VCO непосредственно с выхода детектора фазы результатов в чрезмерном дрожании синхроимпульса. Чтобы исключить дрожание, выход детектора фазы lowpass фильтруется путем накопления его в голосовании. Когда накопленный голос превышает определенный порог подсчета, фаза VCO увеличивается или уменьшается.

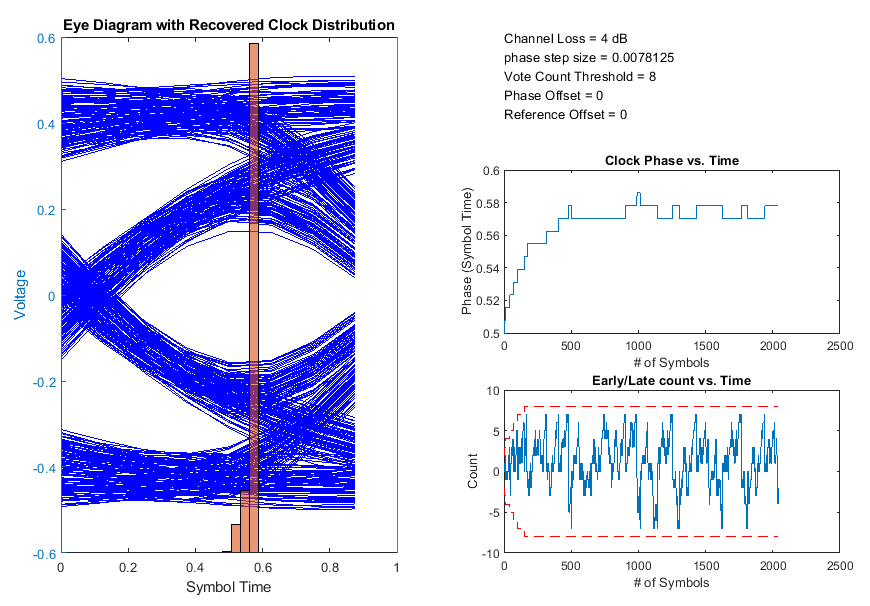

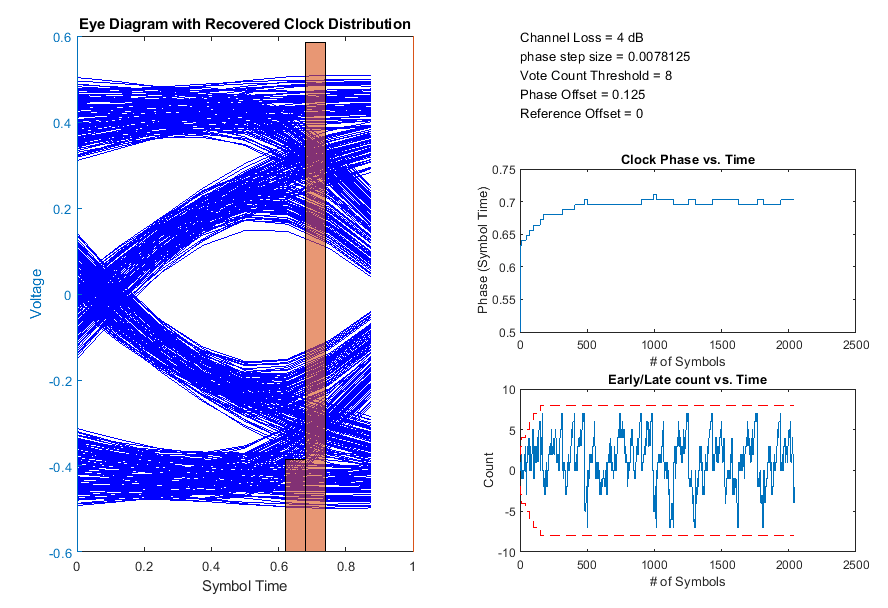

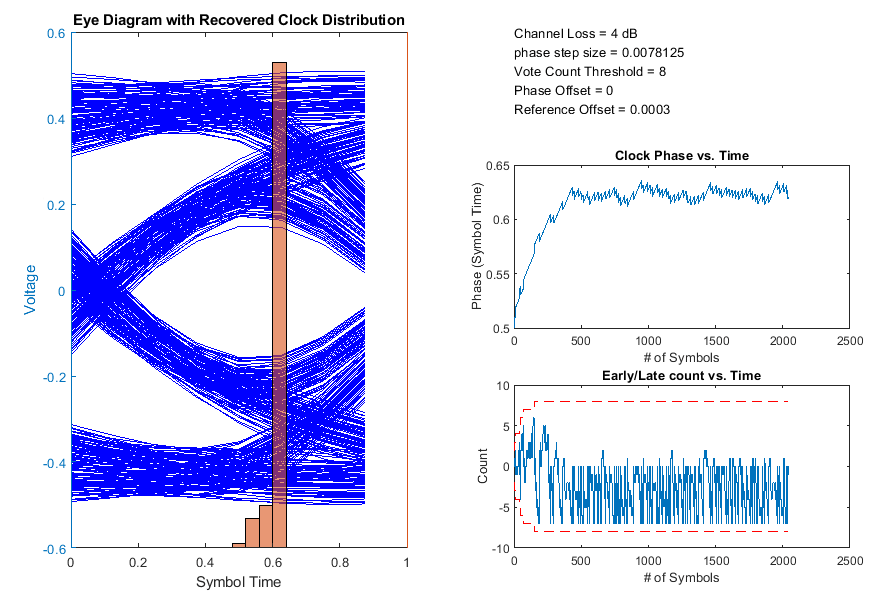

Восстановите синхросигнал из повторяющегося сигнала псевдослучайной двоичной последовательности (PRBS9), не возвращающегося в нуль (NRZ). Рассмотрим, что канал имеет потери 4 дБ, размер шага фазы порог подсчета голосов равен 8, и что нет фазы или опорных смещений.

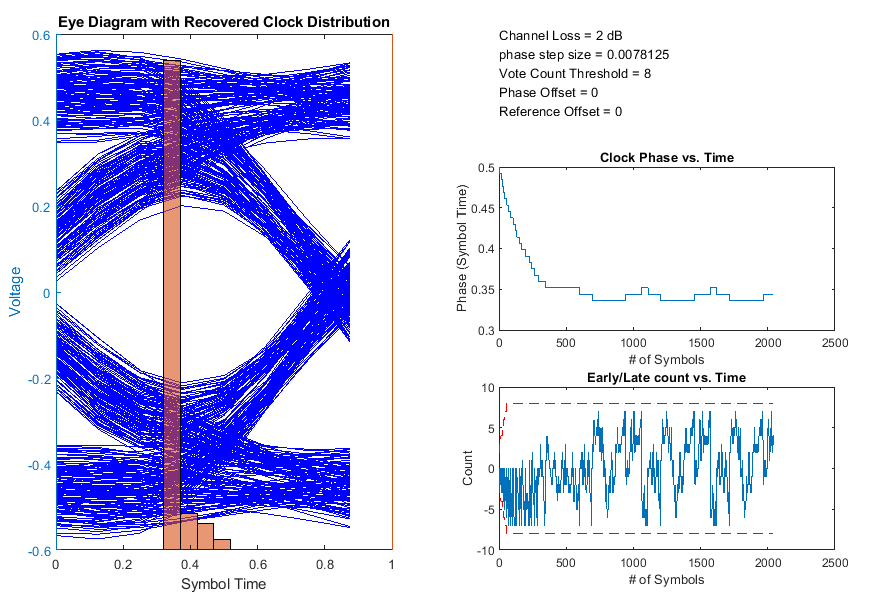

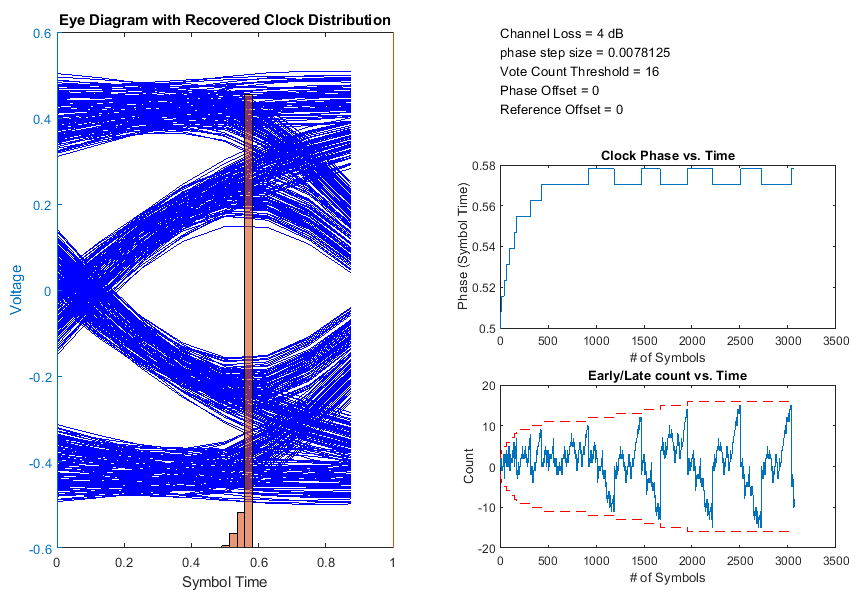

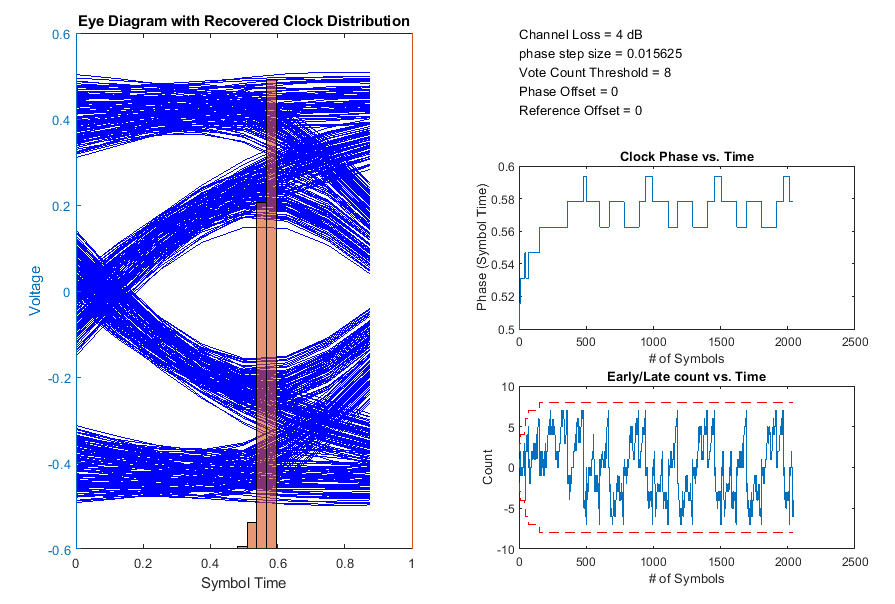

Поведение базовой линии показано с глазковая диаграмма и полученной функции распределения вероятностей синхроимпульса (PDF). PDF очень близко к центру глаза. Фаза синхроимпульса устанавливается между значением 0,5703 символьного времени и 0,5781 символьного времени. Диферирование между этими двумя значениями является следствием нелинейного детектора фазы релейного взрыва и является источником CDR охотничьего дрожания. Чтобы уменьшить величину дитерирования, уменьшите размер шага фазы. Чтобы уменьшить период диферирования, уменьшите порог подсчета голосов.

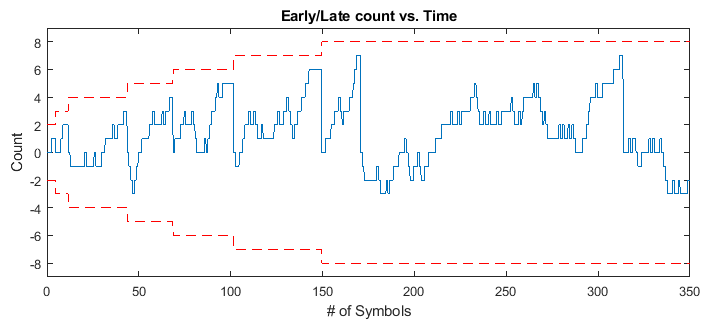

Выходные данные детектора фазы накапливаются при подсчете голосов на раннем/позднем этапе. Когда количество превышает порог подсчета голосов, фаза увеличивается или уменьшается. Чтобы ускорить сходимость CDR, порог отсчета начинается с 2, и каждый раз, когда величина голоса превышает порог, порог увеличивается до тех пор, пока он не достигает максимального количества. Этот рисунок показывает первые 350 символов раннего/позднего подсчета (синий) и порога (штриховая красная линия). Внутренний блок CDR, голос увеличивается или уменьшается, сверяется с порогом и затем сбрасывается при необходимости. Значение внешнего голосования, показанное на рисунке ниже, не касается порога, но становится очевидным, когда голос сбрасывается до 0.

Чтобы показать сходимость синхроимпульса к другой фазе, измените потерю канала на 2 дБ. Фаза синхроимпульса теперь адаптируется к 0,35 времени символа.

Увеличение порога подсчета голосов до 16 приводит к большему периоду диферинга.

Увеличение размера шага фазы до увеличивает сглаживающую величину.

Ручное смещение местоположения дискретизатора данных, когда уравненный глаз не отображает симметрию слева/справа, может максимизировать высоту глаза. Для примера сдвига фазу синхроимпульса вправо времени символа для сдвига выхода синхроимпульса с 0,57 символьного времени до 0,7 символьного времени.

Можно также ввести небольшое количество искажения ссылки тактовой частоты, чтобы реализовать более реалистичный CDR.

[1] Sonntag, J. L. and Stonick, J. «A Digital Clock and Data Recovery Architecture for Multi-Gigabit/s Binary Links». IEEE Journal of Solid-State Circuits, 2006.

[2] Разави, Б. «Проблемы в проектировании схем высокоскоростного синхроимпульса и восстановления данных». Журнал IEEE Communications Magazine, 2002.

CDR | DFECDR | serdes.CDR | serdes.DFECDR