Этот пример показывает верификацию подсистемы путем обеспечения того, что вывод кода ПО в цикле (SIL) совпадает с выходом подсистемы модели. Вы генерируете обвязку верификации SIL, собираете результаты симуляции и сравниваете результаты с помощью инспектора данных моделирования. Можно применить аналогичный процесс для верификации процессора в цикле (PIL).

С помощью SIL симуляции можно проверить поведение производственного исходного кода на вашем хосте-компьютере. С помощью PIL симуляции можно проверить скомпилированные объектные коды, которые вы намереваетесь развернуть в производстве. Можно запустить объектный код PIL на реальном целевом компьютере или на симуляторе процессора.

Если у вас есть Embedded Coder® лицензия, можно создать тестовую обвязку в SIL или PIL режиме для верификации модели. Можно сравнить результаты блоков SIL или PIL с результатами модели и собрать метрики, включая время выполнения и покрытие кода модели. Невозможно собрать покрытие для блоков SIL или PIL. Используя тестовую обвязку для выполнения верификации SIL и PIL, можно:

Управляйте обвязкой с помощью модели. Генерация тестовой обвязки генерирует блок SIL. Эта тестовая обвязка связана с компонентом, находящимся под верификацию. Можно сохранить тестовую обвязку с помощью основной модели.

Используйте встроенные инструменты для этих рабочих процессов тестирования-проектирования-тестирования:

Проверка эквивалентности блоков SIL или PIL

Обновление блока SIL или PIL к последнему проекту модели

Просмотрите и сравните записанные данные и сигналы с помощью Test Manager и Данные Моделирования Inspector.

Когда вы создаете тест эквивалентности, который сравнивает нормальный и SIL или PIL режимы симуляции, для тестирования каждого режима используется отдельная тестовая обвязка. Однако, если вы проверяете эквивалентность атомарной подсистемы или блока Model, одна тестовая обвязка может использоваться как для нормального, так и для SIL или PIL симуляций. Для получения информации о том, когда одна обвязка используется для тестов эквивалентности атомарной подсистемы, см. «Генерация тестов» и «Тестовые обвязки для компонента или модели».

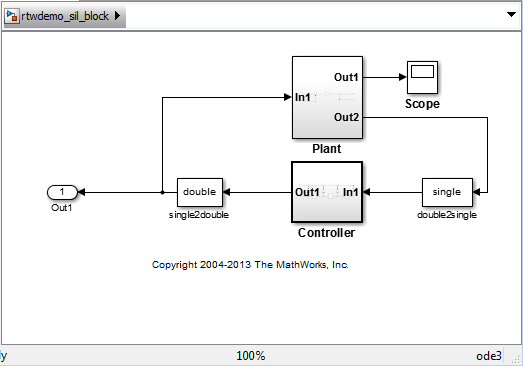

Этот пример моделирует систему контроллера-объекта с обратной связью. Контроллер регулирует выходную мощность объекта выхода.

Создайте обвязку верификации SIL с помощью данных, которые вы регистрируете из системы контроллера-объекта с обратной связью. Подсистема контроллера регулирует выходную мощность объекта выхода. Вам нужна лицензия Embedded Coder для этого примера. Другой способ создать обвязку SIL - это мастер создания теста для компонента модели (см. «Генерация тестов и тестовых обвязок для компонента или модели» и «Создание и запуск обратного теста»).

Откройте модель примера путем ввода

rtwdemo_sil_block

Сохраните копию модели с помощью имени controller_model в новой папке, в расположении с возможностью записи на пути MATLAB.

Включите регистрацию сигнала для модели. В командной строке введите

set_param(bdroot,'SignalLogging','on','SignalLoggingName',... 'SIL_signals','SignalLoggingSaveFormat','Dataset')

Щелкните правой кнопкой мыши сигнал в In1 Controller port и выберите Properties. В диалоговом окне Signal Properties для Signal name введите controller_model_input. Выберите Log signal data и нажмите OK.

Щелкните правой кнопкой мыши сигнал из Контроллера Out1 порта и выберите Properties. В диалоговом окне Signal Properties для Signal name введите controller_model_output. Выберите Log signal data и нажмите OK.

Симулируйте модель.

Получите записанные сигналы из выхода симуляции в рабочую область. В командной строке введите

out_data = out.get('SIL_signals');

control_in1 = out_data.get('controller_model_input');

control_out1 = out_data.get('controller_model_output');Создайте программное обеспечение в цикле тестовой обвязки. Щелкните правой кнопкой мыши Подсистему контроллера и выберите Test Harness > Create Test Harness (Controller).

Установите свойства обвязки:

Name: SIL_harness

Sources and Sinks: Inport и Outport

Выберите Open harness after creation

Advanced Properties – Verification Mode: Software-in-the-loop (SIL)

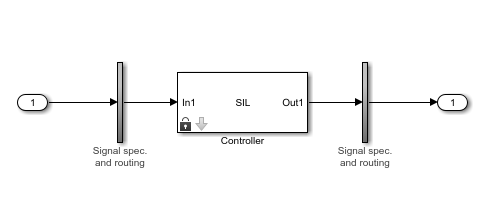

Нажмите OK. Получившаяся тестовая обвязка имеет блок SIL.

Сконфигурируйте и симулируйте обвязку верификации SIL для подсистемы контроллера.

Сконфигурируйте тестовую обвязку, чтобы импортировать записанные входные значения контроллера. На верхнем уровне тестовой обвязки, в диалоговом окне Configuration Parameters модели, на панели Data Import/Export, выберите Input. Введите control_in1.Values в качестве входов и нажмите кнопку OK.

Включите регистрацию сигнала для тестовой обвязки. В командной строке введите

set_param('SIL_harness','SignalLogging','on','SignalLoggingName',...

'harness_signals','SignalLoggingSaveFormat','Dataset')Щелкните правой кнопкой мыши выходной сигнал блока SIL и выберите Properties. В диалоговом окне Signal Properties для Signal name введите SIL_block_out. Выберите Log signal data и нажмите OK.

Симулируйте обвязку.

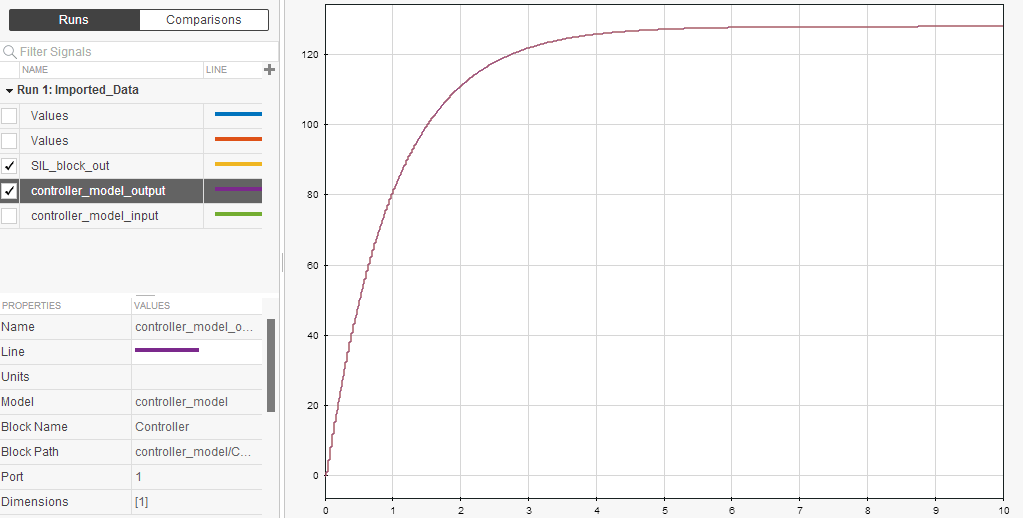

Сравните выходы для обвязки верификации и подсистемы контроллера.

В модели тестовой обвязки, в разделе Review Results, нажмите Data Inspector

, чтобы открыть![]() Данные моделирования Inspector.

Данные моделирования Inspector.

В Данные моделирования Inspector нажмите Import. В диалоговом окне Import.

Установите Import from значение: Base workspace.

Установите Import to значение: New Run.

В разделе Data to import выберите Signal Name для импорта данных из всех источников.

Нажмите Import.

Выберите SIL_block_out и controller_model_out сигналы в панели Runs окна инспектора данных.

На графике отображаются два сигнала, которые перекрываются. Этот результат предполагает эквивалентность для кода SIL. Можно построить график различий сигналов с помощью вкладки Compare в SDI и выполнить более подробный анализ для верификации. Для получения дополнительной информации см. «Сравнение данных моделирования».

Закройте тестовое окно тестовой обвязки. Вы возвращаетесь к основной модели. Значок![]() на блоке Controller указывает, что обвязка SIL связана с подсистемой.

на блоке Controller указывает, что обвязка SIL связана с подсистемой.