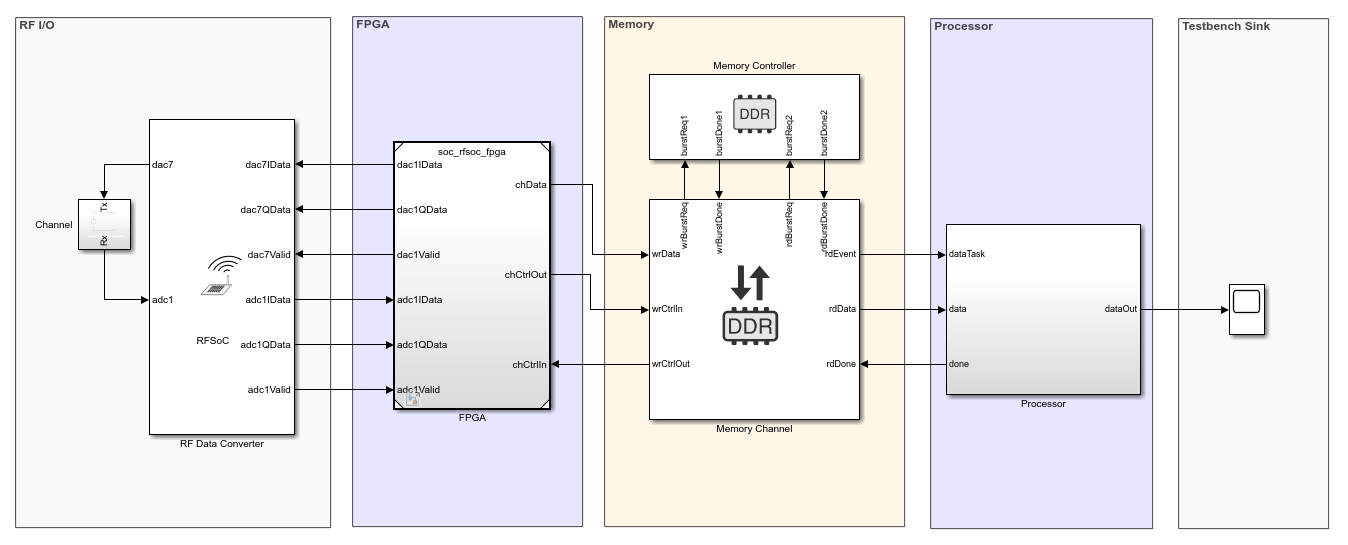

Шаблон RFSoC предоставляет модель симуляции для исходного проекта SoC, доступного из пакета поддержки SoC Blockset™ для Xilinx® Устройства. Используйте этот шаблон для моделирования полного исходного проекта. Анализируйте эффекты внутренней и внешней связности на алгоритмах передачи и приема, таких как поведение памяти и поведение ввода/вывода (RF) радиочастоты.

Чтобы начать работу с моделью SoC Blockset для разработки системы радиосвязи с поддержкой RFSoC, выполните шаги в разделе «Создание модели SoC с использованием шаблона набора блоков SoC». Затем добавьте алгоритмы передатчика и приемника в подсистему FPGA и алгоритм процессора в Подсистему процессора.

DSP System Toolbox™

Пакет поддержки SoC Blockset для устройств Xilinx

Шаблон RFSoC состоит из трех моделей: модели Top, модели FPGA и модели Processor. В модели Top RF Data Converter блок соединяется с блоком FPGA и обеспечивает интерфейс ввода-вывода RF. Блок FPGA реализует алгоритмы приемника и передатчика. Алгоритм FPGA включает в себя блок Test Source, который генерирует синусоидальный сигнал и управляет им на цифроаналоговый преобразователь (DAC) через подсистему Алгоритма передатчика. Подсистема Алгоритма Передатчика реализована как простые сквозные провода, а Подсистема Алгоритма Приемника реализована с помощью логики понижающего дискретизатора. SrcSelReg регистра строения моделируется в FPGA, чтобы выбрать источник данных для подсистемы алгоритма приемника. Процессор записывает регистр SrcSelReg, чтобы выбрать источник тестирования из FPGA или данные RF из аналого-цифрового преобразователя (АЦП) в блоке RF Data Converter. Данные из подсистемы FPGA передаются в Подсистему Процессора через блок Memory Channel. Параметр Channel Type в блоке Memory Channel установлен в AXI4-Stream to software via DMA, который моделирует прямую передачу данных доступа к памяти (DMA) через общую внешнюю память.

Используйте этот шаблон в качестве руководства, заменив подсистемы Алгоритм Приемника и Алгоритм Передатчика в модели FPGA и Подсистему Алгоритма Процессора в модели Процессора на свои собственные функциональные возможности. В этом шаблоне блок RF Data Converter сконфигурирован со специальным RF-интерфейсом, который имеет один DAC (DAC7) и один ADC (ADC1) и цифровой интерфейс I/Q. Количество выборок за тактовый цикл устанавливается равным 2. Путь RF в этом шаблоне закольцован. Если вы хотите использовать различные данные для передатчика и приемника, можно удалить цикл назад и можно предоставить необходимые входные данные в АЦП.

Процессор считывает вычисленные данные из памяти и выполняет дополнительные вычисления (реализованные в шаблоне как сквозной провод). Вы можете просмотреть результаты симуляции, дважды кликнув по блоку Time Scope в подсистеме Testbench Sink.

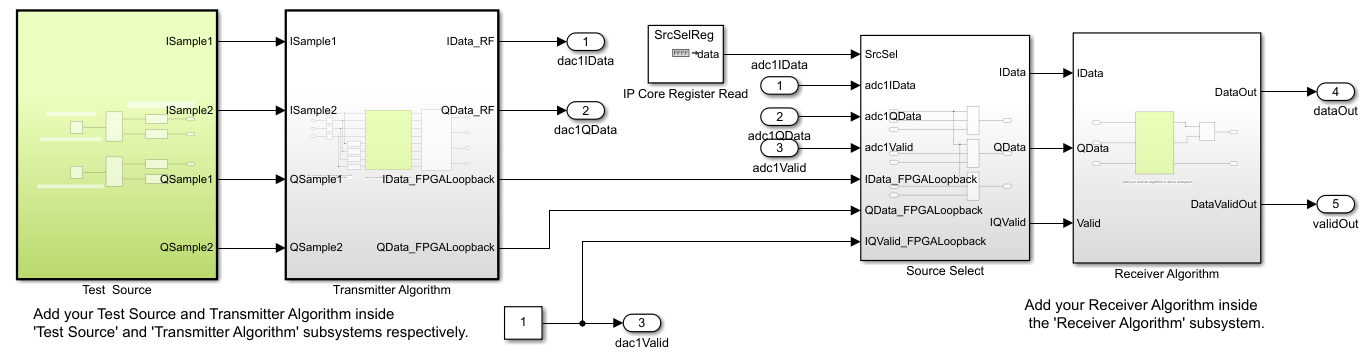

В MATLAB® Панель инструментов, на вкладке Project Shortcuts , нажмите Open FPGA model. Затем откройте подсистему FPGA Tx-Rx Alg Wrapper. Три области выделены зеленым цветом, как показано на этом рисунке. Эти области представляют пользовательский код и расположены в блоке Test Source, подсистеме Transmitter Algorithm и подсистеме Receiver Algorithm.

Модель FPGA включает эти разделы (выделенные зеленым цветом), которые вы должны изменить.

Test Source блок - Этот блок генерирует синусоидальный сигнал 500 кГц и приводит его в подсистему алгоритма передатчика. Измените источник теста в соответствии с вашими потребностями или замените его альтернативным исходным блоком.

Подсистема Алгоритма Передатчика - Содержит подсистему Алгоритма Передатчика, выделенную зеленым цветом. Замените подсистему Tx Algorithm на свой собственный алгоритм передатчика.

Подсистема Алгоритма Приемника - Содержит подсистему Алгоритма RX, подсвеченную зеленым цветом. Замените подсистему Rx Algorithm на свой собственный алгоритм приемника.

IP Core Register Read blocks - Внутри тестируемого проекта (DUT) добавьте эти блоки, чтобы добавить регистры к IP-адресам вашего алгоритма. Инициализируйте этот блок с помощью соответствующего блока Register Write в модели Processor.

Чтобы включить последовательное поведение симуляции, на вкладке Project Shortcuts нажмите Open FPGA model и повторите этот шаг.

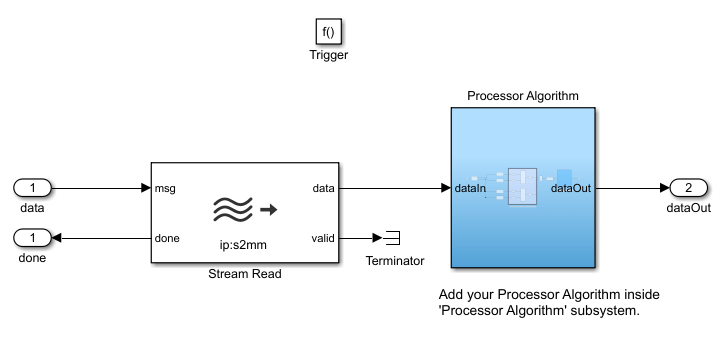

На панели инструментов MATLAB, на вкладке Project Shortcuts , нажмите Open Processor model. Модель Processor содержит обертку алгоритма процессора и подсистемы Initialize Function. Подсистема Processor Algorithm Wrapper подсвечена синим цветом, который представляет пользовательский код для алгоритма процессора. Откройте подсистему Processor Algorithm Wrapper и замените внутреннюю подсистему Processor Algorithm (также выделенную синим цветом) желаемым алгоритмом. Откройте подсистему Initialize Function и добавьте блок Register Write для каждого блока IP Core Register Read, добавленного в модель FPGA.

Используйте шаблон для создания модели SoC