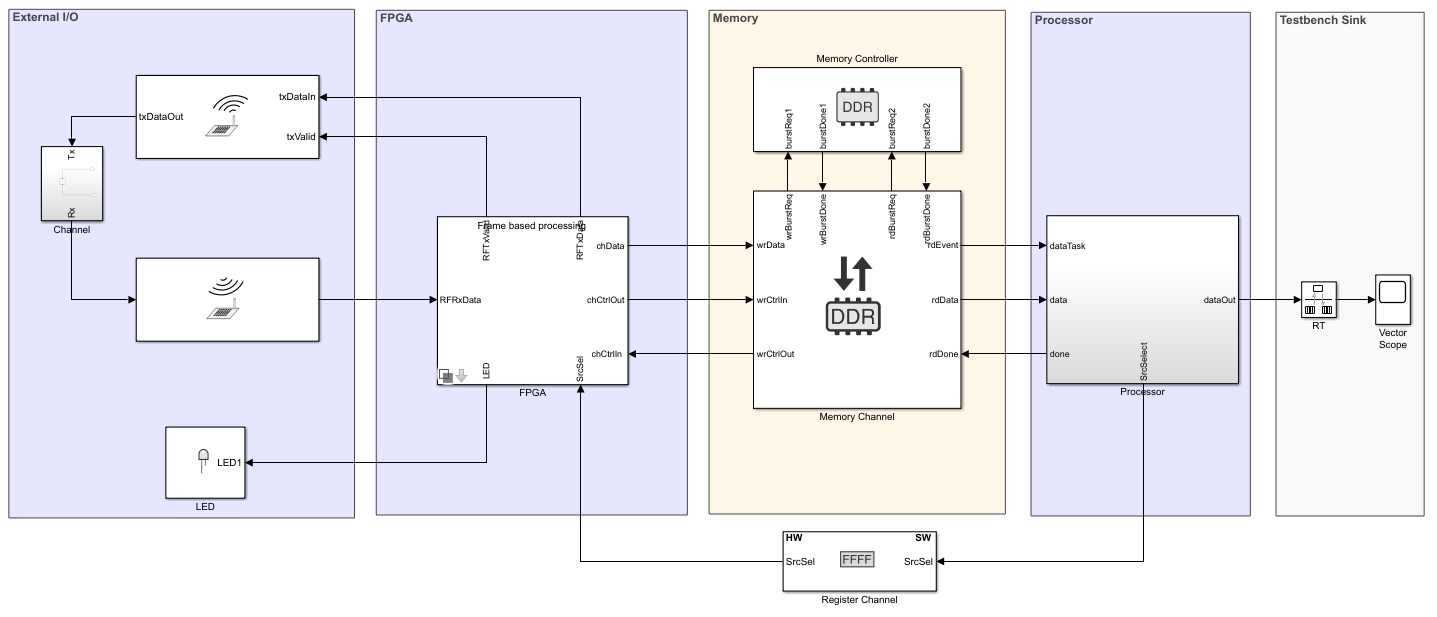

Шаблон программно определяемого радио (SDR) предоставляет модель симуляции для однокристального исходного проекта, доступную из Toolbox™ пакета Communications Поддержку для Xilinx® Zynq®- Базовое радио. Используйте этот шаблон для моделирования полного исходного проекта и анализа эффектов внутренней и внешней связности и алгоритма SDR, таких как поведение памяти и радиочастотный (RF) ввод-вывод поведение.

Чтобы начать работу с моделью SoC Blockset™ для разработки системы SDR, выполните шаги, чтобы Создать модель SoC с использованием шаблона SoC Blockset.

Communications Toolbox

Пакет поддержки SoC Blockset для устройств Xilinx

Этот шаблон моделирует приемопередатчик SDR AD9361 состоящий из блоков передатчика и приемника. Приемопередатчик соединяет RF-канал с FPGA, который реализует приемник и алгоритм передатчика. Алгоритм FPGA включает в себя блок Test Source, который генерирует синусоидальный сигнал и управляет им передатчику. Алгоритм FPGA также включает алгоритм Tx, реализованный как простые проходные провода, и алгоритм Rx, реализованный как блок усиления. Регистр строения, srcSel моделируется в FPGA, чтобы выбрать источник данных для алгоритма Rx. Процессор записывает регистр srcSel, чтобы выбрать источник тестирования из данных FPGA или RF из приемопередатчика. Этот регистр моделируется с помощью блока Register Channel. Данные из алгоритма FPGA передаются в процессор через блок Memory Channel.

Используйте этот шаблон в качестве руководства и замените Алгоритмы RX и Алгоритм Tx в FPGA и Алгоритм Процессора в процессоре своими функциями. Параметр Channel Type памяти установлен в AXI4-Stream to software via DMA, который моделирует прямую передачу данных доступа к памяти (DMA) через общую внешнюю память.

Процессор считывает вычисленные данные из памяти и выполняет дополнительные вычисления (реализованные в шаблоне как сквозной провод). Вы можете просмотреть результаты симуляции, дважды кликнув по блоку Vector Scope в приемнике тестовых данных.

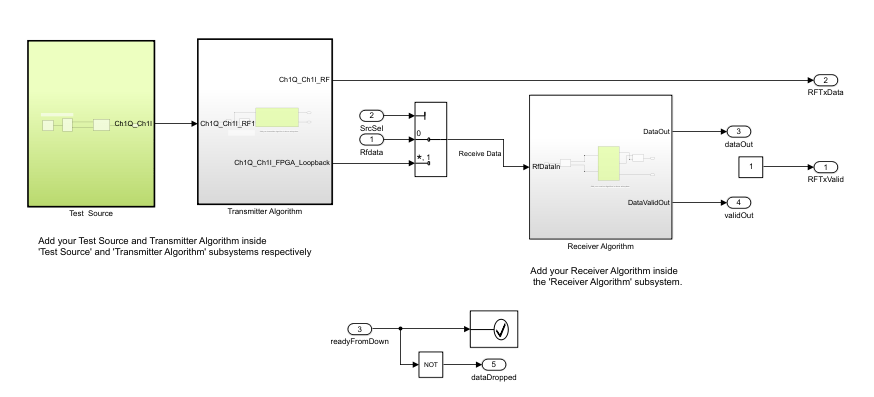

В MATLAB®на вкладке Project Shortcuts нажмите Open FPGA sample model. Затем откройте FPGA Tx-Rx Alg Wrapper. Заметьте три области, выделенные зеленым цветом. Эти области представляют пользовательский код и расположены в блоке Receiver Algorithm, в блоке Transmitter Algorithm и блоке Test Source.

Модель FPGA включает следующие разделы для изменения (выделены зеленым цветом):

Тестовый Исходный блок - Этот блок генерирует 10-kHz синусоидальный сигнал и управляет им к алгоритму передатчика. Измените источник теста в соответствии с вашими потребностями или замените его альтернативным исходным блоком.

Подсистема Алгоритма Приемника - Внутри подсвеченной зеленым цветом подсистемы с именем Rx Algorithm существует блок с меткой Algorithm. Алгоритм принимает данные I/Q как входные и выходные с действительным сигналом. Замените этот блок на свой собственный алгоритм Rx.

Алгоритм передатчика - Внутри подсвеченной зеленым цветом подсистемы с именем Tx Algorithm, алгоритм имеет вход от источника тестирования и два выходных сигнала: один в канал RF и один в FPGA. Замените этот блок на свой собственный алгоритм Tx.

Чтобы включить последовательное поведение симуляции, на вкладке Project Shortcuts нажмите Open FPGA frame model и повторите этот шаг.

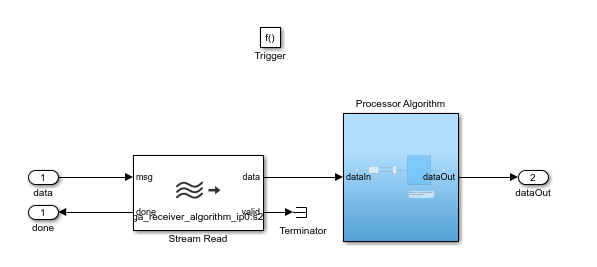

В MATLAB, на вкладке Project Shortcuts , нажмите Open processor model. Подсистема, выделенная синим цветом, представляет пользовательский код для алгоритма процессора. Откройте Processor Algorithm Wrapper и замените внутренний блок Processor Algorithm (также выделенный синим цветом) на требуемый алгоритм.

Верхняя модель шаблона также включает канал регистра для связи между процессором и моделью FPGA. Используйте канал регистра, чтобы сконфигурировать модель FPGA или считать и проверить регистры состояния. Блок Register Channel в шаблоне включает один регистр. Чтобы добавить дополнительные регистры, вы должны изменить параметры блоков канала регистра, алгоритм FPGA и алгоритм процессора:

Добавьте регистры в канал регистра - Дважды кликните блок Register Channel, чтобы открыть маску блока и добавить дополнительные регистры по мере необходимости. Добавление регистров создает дополнительные порты на блоке Register Channel. Для получения дополнительной информации см. раздел Register Channel.

Добавьте порты к модели процессора - Перемещайтесь к модели Processor Algorithm Wrapper. Чтобы перейти к модели процессора, нажмите Open Processor model на вкладке Project Shortcuts. Дважды кликните Processor Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте выходной порт к модулю и добавьте логику, чтобы привести значение к дополнительному выходу. Для регистров чтения добавьте порт входа и логику для обработки информации, возвращенной из регистра чтения. Из верхней модели проводите порт к блоку Register Channel.

Добавьте порты к модели FPGA - перейдите к модели FPGA Algorithm Wrapper. Чтобы перейти к модели обработки на основе FPGA/Frame, нажмите Open FPGA sample model на вкладке Project Shortcuts. Дважды кликните FPGA Algorithm Wrapper, чтобы изменить его.

Для регистров записи добавьте порт входа к модулю и логику для обработки информации, возвращенной из регистра чтения. Для регистров чтения добавьте порт выхода и логику, чтобы привести значение к добавленному порту выхода.

Для эквивалентного поведения при использовании Simulink® вариант на основе выборки, повторите этот шаг для модели обработки на основе выборки в обертке FPGA.

Из верхней модели проводите новый порт к блоку Register Channel.