Вы можете использовать пакет поддержки Vision HDL Toolbox™ для Xilinx® Zynq®-Основанное оборудование для прототипирования алгоритмов зрения на оборудовании на основе Zynq, которое подключено к реальным входам и вывода видео. Используйте пакет поддержки для:

Захват входного или выходного видео с платы и импорт его в Simulink® для разработки и верификации алгоритмов.

Создавайте и развертывайте IP-ядра на плате FPGA. (требует HDL- Coder™)

Сгенерируйте и разверните код С в ARM® процессор на плате. Можно маршрутизировать видеоданные из FPGA в процессор ARM ®, чтобы разработать алгоритмы обработки видео, нацеленные на процессор ARM. (требует Embedded Coder®)

Просмотрите выходы алгоритма на устройстве HDMI.

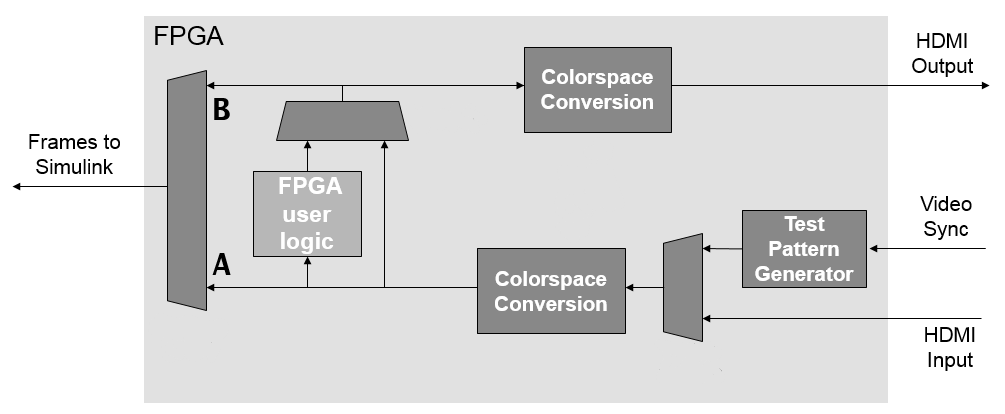

Используя этот пакет поддержки, вы можете захватывать живое видео с устройства Zynq и импортировать его в Simulink. Источником видео может быть вход видео HDMI на плату, генератор тестового шаблона на микросхеме, включенный в исходный проект, или выход вашего пользовательского алгоритма на плате. Вы можете выбрать цветовое пространство и разрешение входных кадров. Разрешение захвата должно совпадать с разрешением вашего входа камеры.

Если у вас есть видеокадры в Simulink, вы можете:

Разрабатывайте основанные на кадрах алгоритмы обработки видео, которые работают на входе живых данных. Используйте блоки из библиотек Computer Vision Toolbox™, чтобы быстро разработать основанные на кадрах алгоритмы с плавающей точкой.

Используйте блок Frame To Pixels из Vision HDL Toolbox, чтобы преобразовать вход в поток пикселей. Разрабатывайте и проверяйте алгоритмы потоковой передачи пикселей, используя другие блоки из библиотек Vision HDL Toolbox.

Пакет поддержки Vision HDL Toolbox для Xilinx Zynq-Based Оборудования предоставляет исходный проект для прототипирования видео алгоритмов на платах Zynq.

Когда вы генерируете HDL-ядро IP для вашего пиксельного потокового проекта с помощью HDL Workflow Advisor, ядро включается в этот исходный проект как FPGA user logic раздел. Точки на A и B на схеме показаны опции для захвата видео в Simulink.

Пользовательская логика FPGA может также содержать дополнительный интерфейс для внешней буферной памяти системы координат, который не показан на схеме.

Примечание

Для исходный проект на устройстве Zynq требуется одинаковое разрешение видео и цветовой формат для всего пути данных. Выбранное разрешение должно совпадать с разрешением входов камеры. Проект, который вы нацелили на пользовательский логический раздел FPGA, не должен изменять формат кадра или цветовое пространство видеопотока.

Исходный проект не поддерживает многопиксельную потоковую передачу.

Запустив всю или часть своего пиксельного потокового проекта на оборудовании, вы ускоряете симуляцию своей системы обработки видео и можете проверить ее поведение на реальном оборудовании. Чтобы сгенерировать HDL-код и развернуть ваш проект на FPGA, вы должны иметь HDL Coder и пакет поддержки HDL Coder для Xilinx Zynq Platform, а также Xilinx Vivado® и Xilinx SDK.

После нацеливания FPGA можно захватить live выходные системы координат из пользовательской логики FPGA обратно в Simulink для дальнейшей обработки и анализа. Можно также просмотреть выходные данные на выходе HDMI, подключенном к вашей плате. Используя сгенерированный hardware interface model, можно управлять опциями захвата видео и читать и записывать порты AXI-Lite на пользовательской логике FPGA из Simulink во время симуляции.

Шаг нацеливания FPGA также генерирует software interface model. Эта модель поддерживает программное нацеливание на оборудование Zynq, включая режим external mode, процессор в цикле и полное развертывание. Он обеспечивает управление путями данных и интерфейс для любых портов AXI-Lite, определенных в целевой подсистеме FPGA. Из этой модели можно сгенерировать код ARM, который управляет или реагирует на порты AXI-Lite на пользовательской логике FPGA. Затем можно развернуть код на плате для запуска вместе с пользовательской логикой FPGA. Для развертывания программного обеспечения на процессоре ARM необходимо иметь Embedded Coder и пакет поддержки Embedded Coder для платформы Xilinx Zynq.