Подготовьте свои целевые платы FPGA к развертыванию нейронной сети для глубокого обучения путем конфигурирования их, чтобы соединиться с хостом - компьютером.

Настраивать плату:

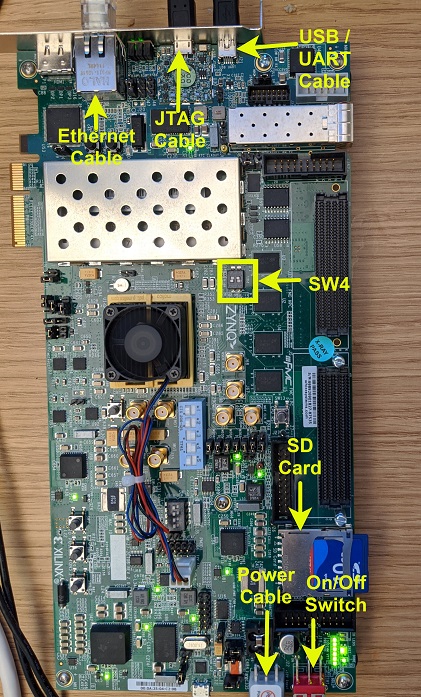

Включите шнур питания, и затем соедините хост - компьютер с платой FPGA при помощи кабеля JTAG.

Задайте SW4 переключите настройки, чтобы использовать интерфейс Digilent USB-TO-JTAG.

| Источник настройки | SW4 переключатель 1 | SW4 переключатель 2 |

| 'none' | 0 | 0 |

| Коннектор кабеля J3 | 1 | 0 |

| Интерфейс Digilent USB-TO-JTAG | 0 | 1 |

| JTAG (управляющий выводом) Заголовок J62 | 1 | 1 |

Эта диаграмма показы параметры конфигурации для Xilinx® Zynq®- 7 000 оценочных плат ZC706.

Чтобы узнать больше о конфигурации платы, см. Руководство пользователя оценочной платы Xilinx ZC706.

Настраивать плату:

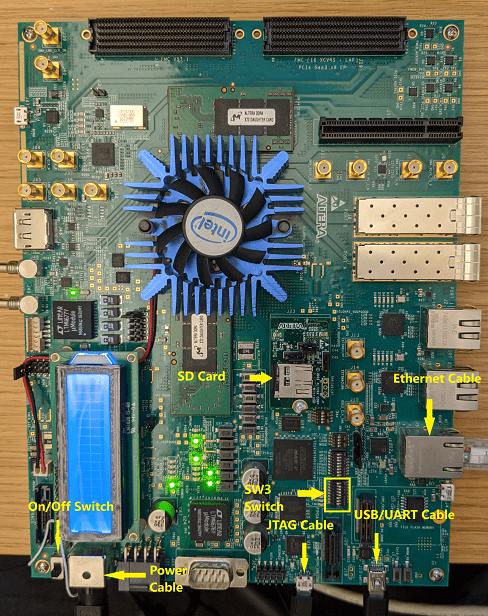

Включите шнур питания, и затем соедините хост - компьютер с платой FPGA при помощи кабеля JTAG.

Задайте настройки переключателя SW3.

| Бит 1 | Бит 2 | Бит 3 | Бит 4 | Бит 5 | Бит 6 | Бит 7 | Бит 8 |

| Off | On | On | On | On | Off | Off | Off |

Соедините две сменных платы DDR4 с пазом плагина памяти.

Эта диаграмма показы параметры конфигурации для Intel® Arria® 10 комплектов разработчика SoC.

Чтобы узнать больше о конфигурации платы, см. руководство пользователя Arria 10 SoC Комплекта разработчика.

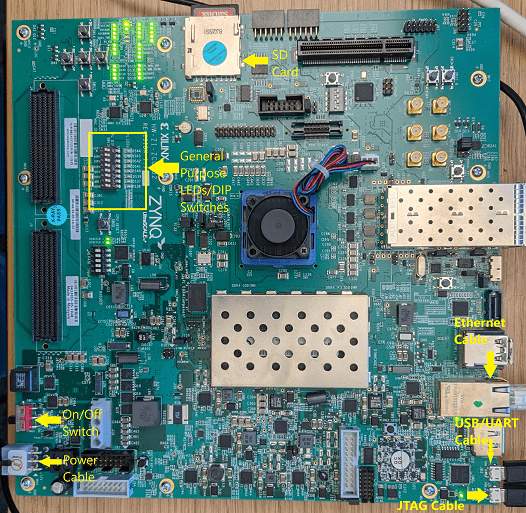

Настраивать плату:

Включите шнур питания. При использовании JTAG соедините плату FPGA с хостом - компьютером при помощи кабеля JTAG. При использовании Ethernet соедините плату FPGA с хостом - компьютером при помощи кабеля Ethernet.

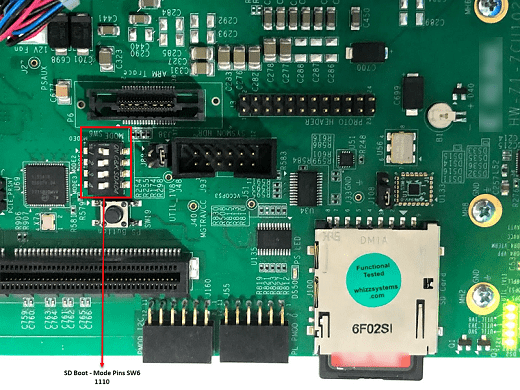

Сконфигурируйте SW6 switch.

| Режим начальной загрузки | Контакты режима [3:0] | SW6 Переключите положение [3:0] |

JTAG | 0, 0, 0, 0 | на, на, на, на |

QSPI32 | 0, 0, 1, 0 | на, на, прочь, на |

SD | 1, 1, 1, 0 | прочь, прочь, прочь, на |

SW6 положением по умолчанию является QSPI32. Для SW6 Dip-переключатель, перемещая переключатель к ON метка 0.

Эта диаграмма показы местоположение SW6 switch.

Эта диаграмма показы параметры конфигурации для макетной платы Xilinx Zynq UltraScale +™ MPSoC ZCU102 FPGA.

Чтобы узнать больше о настройке оборудования ZCU102, обратитесь к документации Xilinx.